Journal list menu

Export Citations

Download PDFs

Issue Information

Research Articles

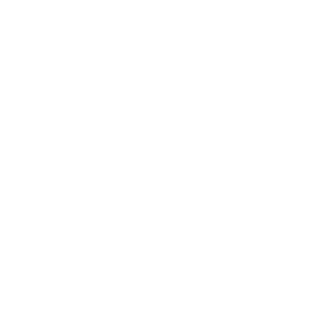

The noise performance of CMOS Miller operational transconductance amplifiers with embedded current-buffer frequency compensation

- Pages: 457-465

- First Published: 29 September 2016

The noise of cascode transistors is usually considered to be negligible. It is demonstrated in this paper that this is not the case for an operational transconductance amplifiers exploiting Miller compensation via an embedded current buffer.

It is shown analytically and by means of simulations that the noise power spectral density of the cascode transistor implementing the current buffer (M6) can be dominant at high frequencies. Its contribution can be of the same order of magnitude as that of the transistors in the first gain stage. This has been found to be the case for frequencies just below the gain-bandwidth product. A simple design equation was found to reduce this effect.

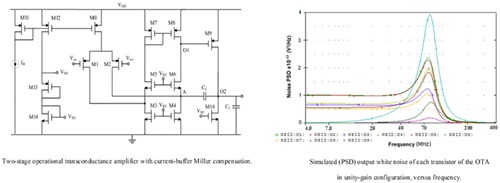

A 0.008-mm2, 35-μW, 8.87-ps-resolution CMOS time-to-digital converter using dual-slope architecture

- Pages: 466-482

- First Published: 06 October 2016

This paper presents a high resolution time-to-digital converter (TDC) for low-area applications. To achieve both high resolution and low circuit area, we propose a dual-slope voltage-domain TDC, which is composed of a time-to-voltage converter (TVC) and an analog-to-digital converter (ADC). In the TVC, a current source and a capacitor are used to make the circuit as simple as possible. For the same reason, a single-slope ADC, which is commonly used for compact area ADC applications, is adapted and optimized. Because the main non-linearity occurs in the current source of the TVC and the ramp generator of the ADC, a double gain-boosting current source is applied to overcome the low output impedance of the current source in the sub-100-nm CMOS process. The prototype TDC is implemented using a 65-nm CMOS process, and occupies only 0.008 mm2. The measurement result shows a dynamic range with an 8-bit 8.86-ps resolution and an integrated non-linearity of ±1.25 LSB.

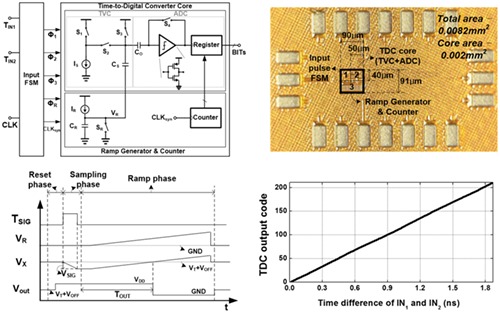

Analysis of a balanced analog multiplier for an arbitrary number of signed inputs

- Pages: 483-501

- First Published: 08 August 2016

We present an extension of the double-balanced current-commutating analog multiplier (also known as the Gilbert cell) that enables the multiplication of an arbitrary number of signed differential input voltages. A general analysis of the circuit for an arbitrary device nonlinearity is provided, and brief simulation and measurement results are reported. Both bipolar and metal–oxide–semiconductor implementations are considered.

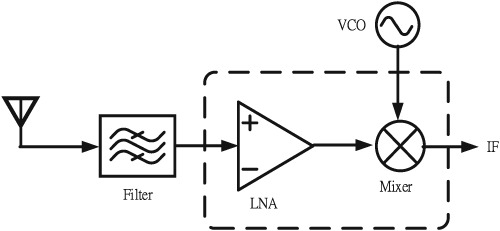

A front-end receiver with a dual cross-coupling technique for MICS applications

- Pages: 502-514

- First Published: 13 July 2016

A front-end receiver featuring low-power design has been presented for Medical Implant Communication Services applications. The dual cross-coupling, gm-boosting, resistive feedback, and current reuse techniques are used to reduce current dissipation and maintain the adequate gain performance. Notably, inductor-less design saves chip area. The radio frequency differential signals are directly coupled to the demodulator. The chip occupies 0.76 × 0.98 mm2, including testing pads, and dissipates only 1.65 mW. To demonstrate the properties of the proposed techniques, the Medical Implant Communication Services receiver has been analyzed, designed, and measured as proof of concept.

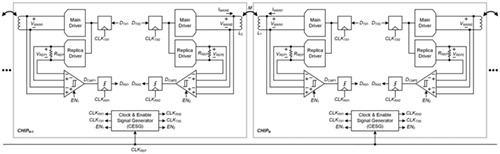

A simultaneously bidirectional inductively coupled link in a 0.13-µm CMOS technology

- Pages: 515-529

- First Published: 05 July 2016

A simultaneously bidirectional inductively coupled link has been developed to provide higher signaling bandwidth for a given inductively coupled channel. Two types of echo signals, that is, the resistive and inductive echo signals, are canceled without an inductive replica load to save silicon area. The resistive echo signal is canceled with a replica driver driving a resistive replica load, while the inductive echo signal is canceled by deliberately controlling the timing of a receiver comparator. The prototype implemented in a 0.13-µm complementary metal–oxide–semiconductor technology occupies 0.019 mm2 including an on-chip channel inductor and shows 9.1-pJ/b energy efficiency at 3.0-Gbps signaling bandwidth, that is, 1.5 Gbps in each signaling direction.

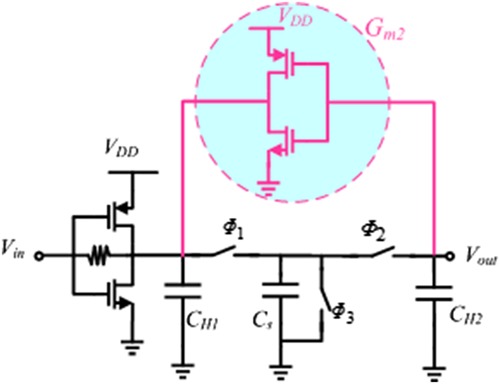

Analysis and design of discrete-time charge domain filters with complex conjugate poles

- Pages: 530-549

- First Published: 25 July 2016

This paper proposes a discrete-time charge domain filter that achieves complex conjugate poles in the transfer function of the filter. To achieve complex conjugate poles, local feedbacks are inserted around two successive discrete-time integrators. Analytical models and circuit-level simulations have been used to verify the behavior of the filter. Simulation results show that a conventional charge domain filter can be simply extended to implement complex conjugate poles while the noise and linearity performance of the filter are also improved.

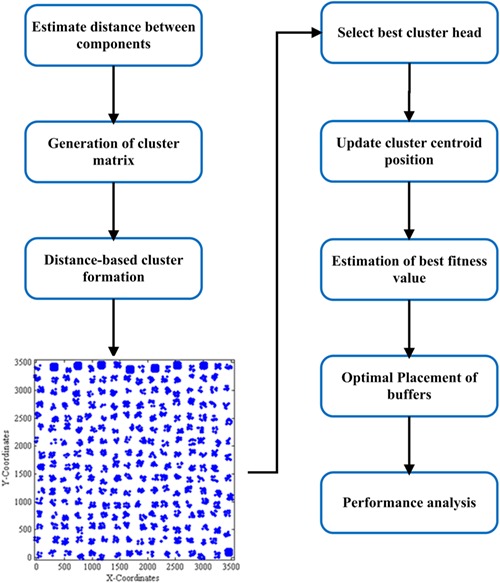

A novel PDWC-UCO algorithm-based buffer placement in FPGA architecture

- Pages: 550-570

- First Published: 24 October 2016

This paper presents a novel Particle Distance Weighted Clustering (PDWC)-Unity Clustering Optimization (UCO) algorithm for the optimal placement of buffers in the Field Programmable Gate Array (FPGA) architecture. A novel PDWC algorithm is applied for clustering the logical components based on the minimum distance between components. A UCO algorithm is developed to determine the optimal location for the placement of the buffers. The overall area and power consumption of the FPGA architecture are reduced because of the optimal buffer placement.

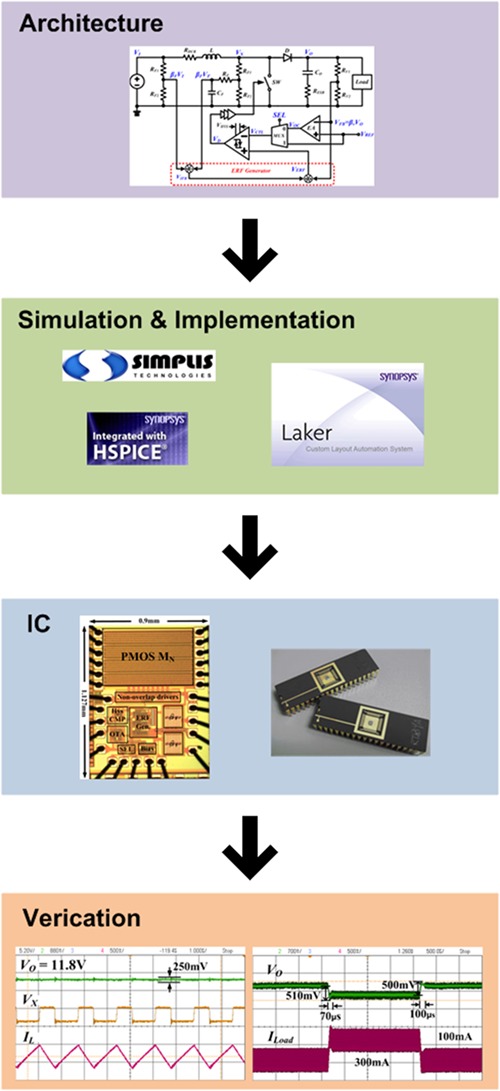

Quasi-V2 hysteretic control boost DC–DC regulator with synthetic current ripple technique

- Pages: 571-591

- First Published: 17 July 2016

This paper presents a current-sensing technique that can compatible with ripple-based control (i.e. hysteretic control and quasi-V2 hysteretic control) boost regulator. This paper has completed design consideration and implementation. Simulation and experimental results are verified by SIMPLIS, HSPICE, and PCB.