High-density implantable neural electrodes and chips for massive neural recordings

Longchuan Wang, Yanxing Suo and Jiahao Wang contributed equally to this work.

Abstract

High-density neural recordings with superior spatiotemporal resolution powerfully unveil cellular-scale neural communication, showing great promise in neural science, translational medicine, and clinical applications. To achieve such, many design and fabrication innovations enhanced the electrode, chip, or both for biocompatibility improvement, electrical performance upgrade, and size miniaturization, offering several thousands of recording sites. However, an enormous gap exists along the trajectory toward billions of recording sites for brain scale resolution, posing many more design challenges. This review tries to find possible insight into mitigating the gap by discussing the latest progress in high-density electrodes and chips for neural recordings. It emphasizes the design, fabrication, bonding techniques, and in vivo performance optimization of high-density electrodes. It discusses the promising opportunities for circuit-level and architecture-level multi-channel chip design innovations. We expect that joint effort and close collaboration between high-density electrodes and chips will pave the way to high-resolution neural recording tools supporting cutting-edge neuroscience discoveries and applications.

Key points

What do we already know about this topic?

-

The law of development in high-density neural recording follows “Moore's law” in neurotechnology, which states that the number of simultaneously recorded neurons doubles approximately every 7 years. Numerous reports have described the design and fabrication strategy to increase the number of channels and performance for recording electrodes and chips. However, the slow pace of neuro tools development still leaves a significant gap in the need for brain-scale studies, and there is a lack of systematic review on both high-density electrode and chip technologies.

What does this study add?

-

To increase the systematic understanding of high-density electrode and chip technologies from different aspects, we review the advancements in formation, fan-out strategy, and high-yield rate achievement of high-density neural electrode arrays. We then discuss the technique improvements in low-noise, area-/power-efficient chips for massive channel neural recording. Finally, we summarize the convergence of emerging technological breakthroughs and discoveries for the next generation of high-density neural recording.

1 INTRODUCTION

Mapping brain activity has been a research hotspot with the launching of various national brain projects worldwide in the last decade. It is of great value for the understanding and treatment of neurological diseases as well as the development of neuromorphic computational methods. Neuroscience today is like chemistry before the periodic table: People knew about elements and compounds but lacked a systematic theory to classify their knowledge.1 The connection of neural networks is further complicated by the complexity of the human brain, which contains an estimated 100 billion neurons, 100 trillion synapses, and 100 chemical neurotransmitters.2 The opening of voltage-gated channels of the neuron would fire action potentials or spikes.3 Understanding what triggers or prevents a neuron from firing is helpful to comprehend how a specific “cell type” processes information and communicates with others.

In recent years, we have witnessed sustained and significant investments in various initiatives globally toward unlocking the human brain.4 To discover mechanisms underlying brain activities and related diseases, an ideal recording tool should be able to detect spikes on multiple sites simultaneously with minimal noise and cellular-scale resolution. It should also be biocompatible to minimize trauma and cover the recording range from a single neuron to its intricate network of connections. This performance relies on the recording density of both electrode sites and chip channels.

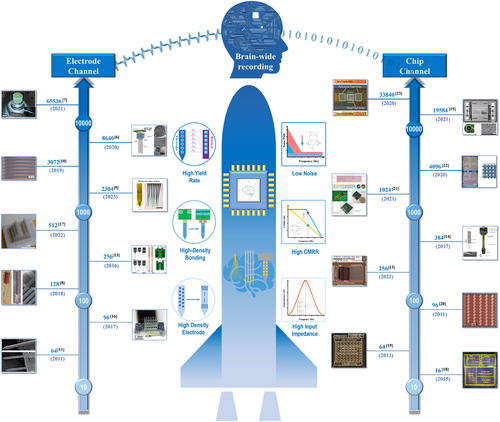

The development of high-density electrodes and chips for neural recording follows “Moore's law” in neurotechnology that the number of simultaneously recorded neurons doubles approximately every 7 years.5 Figure 1 shows that over the past two decades, the number of channels in both electrodes and chips has grown from a few to thousands or even tens of thousands as the technology has evolved. Though fruitful high-density recording techniques exist, the relatively slow pace of neurotechnology development still has a vast gap in the need for exploring brain-scale studies because of the existing and emerging challenges that researchers have never fully addressed.

For electrodes, the challenges include scaling microelectrode size to satisfy a higher density and sampling resolution without expanding impedance or thermal noise,24 increasing recording brain volume without additional tissue damage,25 and packaging the recording electrode array without an increase in size and weight.26 For chips, the search for massive parallel recording channels with high recording quality has never stopped, for example, how to realize the low noise and small-channel crosstalk under restricted silicon area and power consumption. Successfully addressing those challenges would fulfill or even accelerate the pace of “Moore's law” in neurotechnology, enabling the more rapid evolution of brain science.

This review will discuss recent high-density electrodes and chips for massive cellular-scale neural recording for brain-scale studies. This paper first introduces the preparation, packaging, and application limitations of high-density implantable neural recording electrodes and further discusses the technical realization and performance improvement methods for chips for high-density neural recording. It summarizes the advancements in formation, fan-out strategy, and high-yield rate achievement of high-density neural electrode arrays, and the technique progresses in low-noise, area-/power-efficient chips for massive channel neural recording. By bridging the in-depth theoretical and technical breakthroughs between electrodes and chips, the multidisciplinary joint innovation offers a chance for the next generation of neural recording tools.

2 HIGH-DENSITY NEURAL RECORDING ELECTRODES

2.1 The formation of high-density neural electrodes

2.1.1 High-density microwire neural electrodes

Implantable brain-computer interface devices are powerful tools for acquiring high-quality electrophysiological signals post-craniotomy. Since the 1950s, implantable electrodes have undergone several transformations, achieving more diverse signal acquisition. Since the invention of tungsten wire electrodes for neurophysiological recording in the striated cortex of cats in 1959, microwire electrodes have been widely used as traditional implantable brain-computer interface tools in neuroscience research.27 Microwire electrodes are appealing due to their easy preparation, dependable performance, and affordability, making them one of the earliest applied neural microelectrodes. The conductive materials for conventional microwire electrodes are platinum-iridium alloy wire (90% platinum/10% iridium),28 nickel-chromium alloy wire, biomedical stainless steel wire,29 or conductive tungsten wire.30 The insulation layer material is usually made of fluorosilicone rubber,31 polyimide,30 and insulating glass,29 with a single microwire diameter of 15–120 μm.

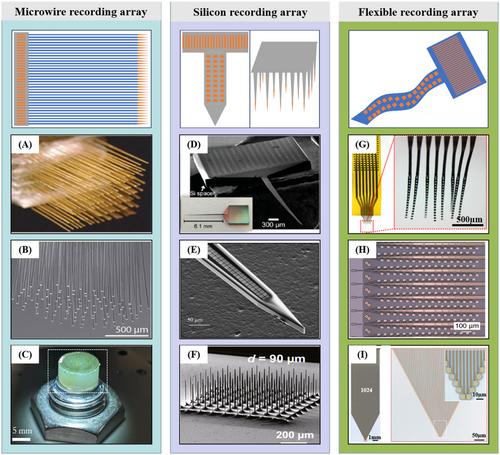

Miguel A. L. Nicolelis et al. assembled micro connectors and microwire electrodes onto customized printed circuit boards and stacked multiple layers of circuit boards to achieve a three-dimensional high-density microwire electrode array of 128 channels, as shown in Figure 2A. They completed an experimental example of recording the activity of a single cortical neuron in a monkey during conscious behavior, successfully recording the discharge signals of up to 247 cortical neurons simultaneously in one experiment.32 On this basis, Abdulmalik Obaid et al. assembled a gold microwire electrode bundle onto a CMOS pixel chip to achieve large-scale parallel microwire electrode arrays for neural signal recording.6 The distribution of the assembled electrode bundle end designed to be implanted in the brain is shown in Figure 2B. The forming process of a large-scale microwire electrode bundle deposits a sturdy glass inorganic insulation layer on a single conductive microelectrode in a thermal oxidation furnace and a sacrificial layer of parylene on the glass insulation layer. This method can adjust the size of the electrode bundle for various models, including high-bandwidth signal acquisition applications ranging from hundreds of channels in small rodents to over 10,000 microwire channels in large mammals. It is suitable for several metal microwire bundles, including Au, W, PtIr, and PtW. Further, it achieved in vivo biological verification based on the type of microwire bundle, which included 1300 microwires with a diameter of 10 mm simultaneously recording the discharge signals of 791 independent neurons in the rat cortex and over 30,000 microwire electrodes recording local field potential signals in the sheep auditory cortex.7 Figure 2C is the macroscopic optical image of the microwire array.

Formation of high-density neural electrodes. (A) Hand-assembled 128-channel microwire electrode array. (B) Distal (brain) end of microwire bundle designed to record in tissue. (C) High-density recording array of 65,536 microwires. (D) SEM and stereoscope (inset) image of a 256-channel Michigan-style probe. (E) SEM of the tip of a shank with two columns of 100 rows each, and (F) High-density silicon microneedles formed by a two-step deep silicon etching process. (G) Photos of a 128-channel type-I NET module. The red dotted box highlights the released front end. (H) High-density “Tree” polymer probes with 32 electrode contacts on one shank. (I) 1024 flexible neurotassels and zoom-in view of the microelectrode filaments. Panels reproduced with permission from (A) PNAS, (B) AAAS, CC-BY-4.0, (C) IOP Publishing, (D) ACS Publications, CC-BY-NC-4.0, (E) IEEE Xplore, (F) Springer Nature Ltd, CC-BY-4.0, (G), Springer Nature Ltd, (H) Elon Musk, Neuralink, CC-BY-ND-4.0, (I) AAAS, CC-BY-NC-4.0.

In addition, a linear 8.4 μm diameter 16-channel carbon fiber wire array was developed for single-unit recordings.33 In fact, as a simple neural signal recording device, microwire electrodes have high practicality and wide application range and have promoted the development of neuroscience in the previous decades. The limitation of microwire electrodes is that a single microwire only contains one neural recording channel. Although inserting a microwire with a diameter of less than 20 μm hardly causes observable damage to brain tissue due to the presence of the nail bed effect, the implantation of large-scale microwires can cause additional depressions on the surface of the brain and compress the brain tissue, resulting in a significant increase in implantation damage.34 In addition, the formation of high-density microfilament electrode bundles depends heavily on manual assembly, which limits the potential of microwire electrodes to further expand toward higher-density neural signal recording.

2.1.2 Silicon-based high-density electrodes

In 1970, Kensall D. Wise et al. first utilized the processing and manufacturing technology of the integrated circuit industry to implement silicon-based planar neural microelectrodes, also known as Michigan-style probes.33 Silicon-based planar neural probes include passive and active devices.

For the passive devices, multiple neural signal recording sites can fit on a single planar probe using micromachining technology, allowing for a larger span to match neuron density in the brain. Based on this arrangement, Michigan-style probes containing 16, 32, or 64 channels have been continuously developed for single neuron recording, studying the projection of neural circuits and the regulatory mechanisms of the cerebral cortex.35-38

In addition, companies like NeuroNexus Technologies, Inc., Diagnostic Biochips, Inc., and Microprobes for Life Science have developed silicon neural probe products to promote better neuroscience and brain science research. The key to improving the density of silicon-based planar neural probes lies in achieving finer-sized metal wires on limited-width (∼100 μm) silicon shanks, which strongly depends on the specific formation process flow of the leading wire.24 Currently, two methods achieve wire widths in the hundreds of nanometers required for high-density recording sites on narrow shanks. First, they prepared the probes on SOI wafers using a commercial state-of-the-art semiconductor foundry with a hybrid Complementary Metal–Oxide–Semiconductor/Micro-Electro-Mechanical System (CMOS/MEMS) process. The key process involves shaping metal wires using ultraviolet (193 nm) lithography technology in CMOS lines. Using a 0.13 μm CMOS process node, Liane Klein et al. achieved one-on-one conduction of 128 signal recording sites (20 × 20 μm2) in a silicon neural shank with a width of 100 μm.8, 39 Gustavo Rios et al. utilized a 248 nm deep ultraviolet stepper lithography machine to achieve 256 channel signal recording sites (8 × 16 μm2) in a single neural shank, as shown in Figure 2D. To further enhance the recording density of silicon-based neural probes, they stacked four two-dimensional planar neural probes with four shanks to create a modular and scalable three-dimensional chronic neural recording microelectrode array. The number of signal recording sites increased to 1024 channels.40 In addition, by assembling micro-optical fibers, they achieved a 3D high-density neural microelectrode array with optoelectronic integration.37

An alternative method for shaping metal wires is using electron beam lithography (EBL) technology. Jörg Scholvin et al. utilized a high electron beam lithography process with a feature size of 200 nm to effectively reduce the linewidth of a single metal wire and significantly increase the density of the wires on a finite shank width.24 The arrangement of the recording sites and dense wires on a single shank is shown in Figure 2E. At present, this study is concerned with enhancing manufacturing techniques. However, there has been limited investigation into the probe's extended in vivo recording capabilities. Since the silicon-based planar probe-type neural microelectrode can reach up to 1 cm in length, it is better suited for obtaining neural signals from the deep brain. However, deep brain implants of silicon-based probes lead to greater implant damage.

To further improve the integration of devices, Changhyun Kim et al. proposed a 64-site multiplexed low-profile neural probe with on-chip CMOS circuitry on the probe base.41 As the technology continues to iterate, silicon probes with CMOS circuitry on the probe shank itself were pioneered initially by Karsten Seidl et al.42 and Tom Torfs et al.43 to realize high-density and electronic depth control in the intracortical neural recording. On this basis, the Interuniversity Microelectronics Centre (IMEC) developed the highly successful Neuropixels CMOS probes. In the meantime, many successors are on the market, for example, the simultaneous neural active pixel sensor CMOS-probe (SiNAPS) from NetS3 Lab, Genova,44 and the 0.00378 mm2 scalable neural recording front-end for fully immersible neural probes based on a two-step incremental Delta-Sigma converter from University of Freiburg.45

Norman's team from The University of Utah created the Utah Electrode Array (UEA), another out-of-plane neural probe array of silicon.46 They produced the array by processing 3 mm thick silicon wafers to create a 10 × 10 microneedle array. They then used lithography to shape the bonding pads of each microneedle channel at the back end. Silicon microneedles are commonly less than 2 mm long and suitable for cortical neural signal recording.46 Hyeonhee Roh et al. optimized the formation process of silicon microneedles using a two-step deep silicon etching process based on the structure of Utah electrodes.47 They prepared a high-density and high aspect ratio silicon microneedle array with 625 channels mm−2 on a silicon wafer. As shown in Figure 2F, this microneedle is 25 times denser than a conventional Utah electrode. Though silicon-based neural recording arrays allow for convenient implantation in various brain regions, their high Young's modulus can cause significant damage.48

2.1.3 Polymer-based high-density flexible electrodes

The flexibility of implanted neural electrodes provides a promising approach to mitigate the challenges associated with rejection reactions between implant and tissue electrode interfaces.49 Therefore, research on preparing flexible polymer-based neural electrodes has quickly gained attention among researchers. Implantable flexible mesh electrodes,50 injectable neural electrodes,25 neuron-like flexible electrodes,51 and flexible neural probes52, 53 have been developed and applied to brain science research. In response to the demand for large-scale high-density parallel neural signal recording, Zhengtuo Zhao et al. used SU8 photoresist as a flexible substrate layer to prepare a 128-channel ultra-flexible high-density neural probe with a thickness of only 1 μm for a single device, as shown in Figure 2G, and implanted 18 probe modules, totaling 2304 channels, to monitor the action potentials of behavioral mice and rats simultaneously. The probe modules achieved the recording of approximately 1000 neural units per cubic millimeter and stable electrophysiological recordings of thousands of neurons for several months.9 Similarly, Xueying Wang et al. employed a three-layer metal wiring technique on a SU8 substrate to create a single probe containing 2640 flexible electrode channels.54 Polyimide (PI) is a flexible packaging material that has been in use for a long time. It has excellent chemical inertness and electrical insulation, and its thermal expansion coefficient matches that of silicon. The research team at Neuralink has successfully used stepper lithography technology to pattern metal layers on PI substrates. This work produced a flexible probe array with a high density of up to 3072 microelectrodes spread across 96 shanks, as shown in Figure 2H.10 Jason E. Chung et al. stacked 16 PI-based flexible electrode modules to assemble a 1024-channel three-dimensional flexible neural probe array, achieving long-term stable neuronal signal acquisition for up to 5 months.21 In addition, Shouliang Guan et al. created flexible neurotassels with 1024 channels on the PI substrate, as illustrated in Figure 2I. Zhejun Guo et al. developed a device with five metal layers and 1024 channels using a multi-layer polyimide exposure process.55 Researchers also fabricate high-density flexible neural probes using multi-layer metal wiring on Parylene substrates.56 Based on the analysis above, we infer that for flexible high-density planar neural probes made of polymers such as SU8, PI, or Parylene, the dense wire arrangement on a limited width can be increased through the application of stepper lithography to decrease the exposure line width. Alternatively, multi-layer metal wiring can increase the wiring density over a limited width, but this method will significantly increase the thickness of the implanted shank.57 There is no doubt that high-density flexible electrodes are the optimal path to achieve long-term in vivo high-density neural signal recording, but their high-density packaging and long-term performance in vivo still need further research.

2.2 Bonding method for high-density neural electrodes

The bonding method of high-density pad arrays is necessary for utilizing the functions of high-density microelectrodes and achieving long-term stable service. The bonding pads for neural probes typically range from tens to hundreds of micrometers. Various available techniques extract and bond a few electrode pads making it relatively simple. However, simultaneously bonding hundreds or thousands of these arrays on passive neural microelectrodes is a highly complex task. Despite being a critical aspect of neural probe research, most articles lack detailed information on packaging and provide relatively little summary data. Thus, a systematic review of bonding methods for high-density microelectrode arrays is necessary to address this gap.

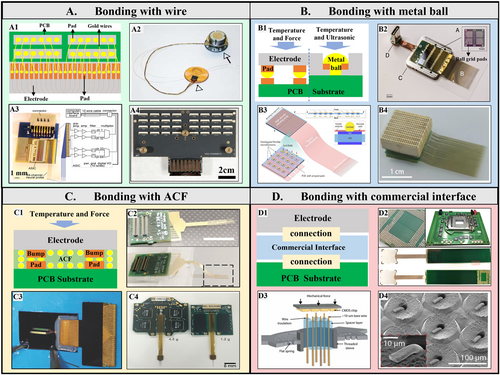

Wire bonding is a technique that uses thin metal wires and a combination of heat, pressure, and ultrasonic energy to tightly solder metal leads to substrate pads shown in Figure 3A1. This process helps achieve electrical interconnection between chips and substrates, allowing information exchange. The lead wires used in wire bonding are aluminum, copper, silver, or gold and come in different diameters ranging from less than 10 μm to hundreds of micrometers to suit various application requirements. Three common types of wire bonding positioning platform technologies used in the industry are hot-pressed wire bonding, wedge ultrasonic wire bonding, and thermoacoustic wire bonding.

Bonding method of high-density neural electrodes. (A1) The schematic of electrode bonding with wire. (A2) An insulated Au wire conducts a Utah electrode individually. (A3) A fully integrated 64-channel recording system and (A4) single 1000 channels Michigan style probe bonding with Au wires. (B1) The schematic of an electrode bonding with a metal ball. (B2) A packaged high-density flexible neural probe bonding by ball grid array. (B3) Schematic and (B4) 1024-channel flexible neural microelectrodes fan-out via modified gold-ball bonding. (C1) The schematic of bonding with ACF. (C2) A parylene flexible probe bonding to PCB and (C3) a polyimide flexible probe bonding to flexible cable via ACF. (C4) ACF bonding also applies to the packaging of a high-density 256-channel rigid silicon electrode. (D1) The schematic of bonding with the commercial interface. (D2) A 1024-channel electrode bonded on the extender PCB compatible with CPU LGA sockets. (D3) The microwires are mechanically lowered onto the CMOS chip until they achieve high connectivity. (D4) SEM of bare microwires are mechanically crimped to contact with a nonplanar pixel surface. Panels reproduced with permission from (A2) Springer Nature Ltd, (A3) PLOS, CC- BY-NC-4.0, (A4) IEEE Xplores, (B2) Elon Musk, Neuralink, CC-BY-ND-4.0, (B3 and B4) Huiling Zhang, Yang Wang, bioRxiv, (C2) Wiley, CC-BY-3.0, (C3) Springer Nature Ltd, (C4) ACS Publications, CC-BY-NC-4.0, (D2) AAAS, (D3 and D4) AAAS, CC-BY-4.0.

Researchers ensure that neural electrodes are safe in biological applications by using gold wire for wire bonding during the bonding process. This process involves high temperature, pressure, and energy generated by ultrasound, which requires a hard substrate for bonding. Wire bonding is a common technique for bonding high-density silicon Utah electrodes. In this approach, the pad arrays situated on the backside of the Utah electrode are led out individually through a gold wire, and the other end of the gold wire attaches to the feedthrough connector, as shown in Figure 3A2.58 The bonding of microelectrodes for neural signal recording in the Michigan-style probe used thermoacoustic wire bonding.59 Figure 3A3 demonstrates a nanofabricated neural probe bonded to a printed circuit board (PCB) containing an application-specific integrated circuit (ASIC) and forming a fully integrated 64-channel recording system.11 Wire bonding extends to the application of high-density neural probes. Justin L. Shobe et al. fully assembled a 1024-electrode 3D microprobe combining four PCB layers, each containing a 256-electrodes array, and they applied Au wires to connect the contact pads.40 In the wire bonding process, proper insulation between the wires is crucial. This factor guarantees the independent operation of each recording channel. After the bonding, researchers often use a biocompatible epoxy resin to insulate the gold wires. Some wires come with an insulation layer. Figure 3A4 shows an overview of the implementation of Michigan-style probes with thousands of channels based on wire bonding. However, the wire bonding method has a low utilization rate on the base area of the probe, which is further expanded by the larger flat flexible cable (FFC) interface.24 This expansion is not conducive to the development of small rodent experiments. Therefore, it is necessary to use the higher-density bonding method from the integrated circuit (IC) industry to package the high-density neural microelectrodes.

The metal ball has unique advantages in the interconnection of planar neural electrodes and planar substrate, as illustrated in Figure 3B1. The industry commonly uses thermal reflow bonding for high-density ball grid arrays (BGA). The bonding of 256 flexible electrodes and PI cable used BGA flip chip bonding technology, with a single SAC305 solder ball diameter of 60 μm.54 Figure 3B2 demonstrates a BGA-packaged device containing 12 chips totaling 3072 channels for the high-density flexible probe.10 High-density pad array conduction is possible by embedding metal bumps into the electrode pads. One effective method is to prepare gold bumps on the substrate using a polymer ultrasonic-on bump (PUB) technique. A customized ultrasonic bonding tool called the Waffle tool applied ultrasonic energy to the bonding area after aligning the electrode pad with the convex point. This method resulted in bonding conduction between the substrate and the electrode at an ultra-low temperature (<100°C) and with a small spacing of only 100 μm.60 Huiling Zhang et al. developed an improved gold ball embedding bonding method,61 which reduces the bonding area by creating a hole in the center of each electrode pad, as shown in Figure 3B3. This method connects flexible electrodes and PCB pads due to its ultra-thin and supple nature. The bonding of gold balls enables this method, while the overlapping placement of flexible fine wires further reduces the bonding area. Improved utilization results in a bonding area of almost 1 cm2 with 1024 channel electrodes. 1024-channel flexible neural microelectrode fan-out appears in Figure 3B4. The bonding effect of metal balls is significantly affected by their size, material, planting method, and bonding conditions, which requires further research.

High-density pad array bonding with anisotropic conductive adhesive (ACF) is another neural electrode array bonding method. ACF is a specialized adhesive used in electronic component packaging. It can conduct electricity in a vertical direction while remaining non-conductive horizontally. Compared with solder reflow used for conventional flip-chip bonding, ACF bonding is a more convenient conduction mode because it only requires a thin adhesive to be applied to the bonding area, as illustrated in Figure 3C1. Another advantage of the ACF bonding over the conventional flip-chip bonding with solder reflow is that the ACF is readily under-filled with non-conductive, spreadable resins; no additional under-filling is necessary. This unique characteristic makes it ideal for use in the high-density bonding of neural microelectrodes. Researchers have already applied ACF for the bonding of a parylene flexible probe62 (Figure 3C2) and a polyimide flexible probe63 (Figure 3C3). Deep silicon etching to create a protruding structure of the solder pad enhances the vertical conductivity of ACF.36, 64 This technique results in the connection between a high-density silicon neural probe and flexible cable, as well as the successful bonding of a 256-channel silicon-based neural probe and a PCB using ACF, as illustrated in Figure 3C4.12 Furthermore, Euisik Yoon developed a bespoke flip-chip bonding technology that utilized ACF. This technique allowed for precise bonding between the CMOS IC and the electroplated Ni/Au bump of the flexible probe.13 While the bonding density of ACF is high, its strength is relatively low. Moreover, temperature and humidity significantly affect the bonding area, and there is a high probability of collisions between nearby channels during a long-term in vivo application.

High-density electrical interfaces are popular in commercial applications, such as the connection interface of a central processing unit and the interface of camera imaging pixel array chips. Over the years, they have undergone multiple technological advancements, resulting in benefits like customization, miniaturization, and high stability. These interfaces also play a vital role in bonding high-density neural electrodes; its schematic appears in Figure 3D1. Shadi A. Dayeh and his team utilized a Land Grid Array (LGA) that was specifically designed for Intel's Sandy Bridge computer processor, along with the LGA1155 CPU slot, to achieve high-density flexible electrode array bonding,65 as shown in Figure 3D2. They used PET as a mask to complete the visualization of conductive silver paste on the LGA solder pad. Nicholas A. Melosh and his research team utilized the imaging array chip of the Xenics Cheetah camera, which uses 327 k pixels, to establish a bundled chip interface with a spacing of 20 μm and a pixel size of 10 × 10 μm. This interface enabled the alignment and pairing of thousands of channels of gold microwire electrode bundles and pixel arrays. After pairing, reliable mechanical compression curls the tail end of the microwire and bonds it to the chip pad, as shown in Figure 3D3. The connectivity of the microwire to the pixel is measured by the conductivity and noise characteristics of each pixel, indicating that over 90% of the microwires can be connected to the pixel chip through conduction. The mechanically crimped microwires appear in Figure 3D4.6 This method is further extended and applied to bond 65,536 channel microwire electrodes.7 However, the customization of commercial interfaces is limited to a single type of neural electrode, which limits their scope of application.

2.3 High yield rate achievement of high-density neural electrodes

When implanting electrodes with a higher number of recording channels, factors such as impedance performance, biocompatibility, implantation process, and long-term stability are crucial in achieving high yield rates for in vivo neural recording. Scott F. Lempka et al. verified through theoretical analysis that recording the amplitude and noise of neural elements depends on the selected recording bandwidth and the effect of electrode-tissue interface impedance recording density and discharge rate of neurons around the electrode.66 With the increase in the number of high-density electrodes, arranging more recording sites on probes with limited width and length will inevitably lead to a decrease in the size of recording sites.24 However, reducing the size of implants and recording sites will increase impedance.67 Although the smaller recording sites improve the difference between the waveform of the nearest single neuron and other nearby action potentials, the increase in impedance leads to a decrease in signal amplitude and an increase in noise level. This change makes it increasingly challenging to distinguish action potentials from high-amplitude noise.68 To address this issue, they altered the surface materials of traditional metal microelectrodes to enhance roughness and decrease electrode impedance values. Researchers use various methods to modify these materials, such as magnetron sputtering iridium oxide,69 titanium nitride,14 electrochemical electroplating of platinum black,70 conductive polymer PEDOT/PSS.71 Modifying thousands of microelectrodes and ensuring impedance consistency performance are critical for high-density neural recording arrays and will bring more challenges to the design of the input impedance of the acquisition circuit amplifier.

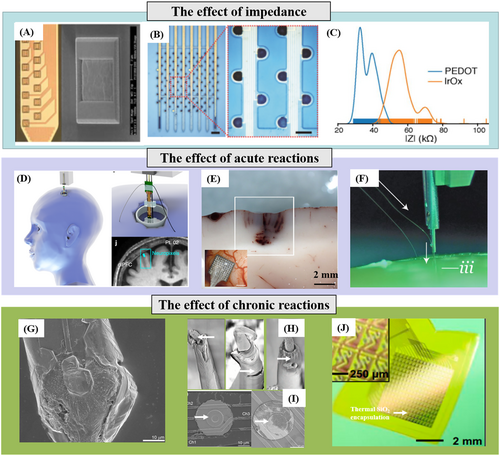

James J. Jun et al. developed a fully integrated silicon probe with 960 CMOS processing-compatible low-impedance Titanium Nitride (TiN) sites for high-density recording of neural activity. The 960 TiN recording sites with impedance at 1 kHz were 149 ± 6 kΩ and formed using the sputtering method, as shown in Figure 4A.14 Shouliang Guan et al. achieved synchronous electroplating of 120 channels of platinum black by shorting several electrode interfaces through customized electroplating connectors,63 as shown in Figure 4B. After electroplating, the impedance of the microelectrodes decreased from 1MΩ to about 100 kΩ at 1 kHz, with a yield of 90.1 ± 5.1%. They also used the electrochemical electroplating method to modify 1024-channel silicon-based electrodes.12 Neuralink modified high-density recording sites through iridium oxide (IrOx) sputtering and PEDOT/PSS electroplating, achieving impedance reduction to 56.46 ± 7.10 kΩ and 36.97 ± 4.68 kΩ10 respectively, as illustrated in Figure 4C. The impedance performance of various microelectrodes also showed significant differences.

Yield rate of a high-density neural electrode array. (A) Photograph of a shank with multiple TiN sites in a Neuropixels probe. (B) Images of microelectrodes after platinum black deposition. (C) Distribution of electrode impedances for two surface treatments: poly(3,4-ethylenedioxythiophene) and IrOx. (D) 3D model of the deep brain stimulation burr hole location with a model of the high-density Neuropixels probe and with the putative Neuropixels location overlaid on the pre-operative magnetic resonance imaging (top) during one deep brain stimulation case. (E) Detail of the petechial hemorrhages after acute UEA implantation in the human brain. (F) The image of the inserter approaches the brain proxy with a thread. (G) SEM of the recording site shows substantial cellular encapsulation. (H) Post-explant SEM of individual microwire to indicate deterioration in electrode insulation for parylene-C coated Pt/Ir microwires. (I) SEM of the recording site shows complete trace degradation around the recording site in a silicon probe. (J) Photograph of a platform of active multiplexed flexible electronics with double-sided thermal SiO2 encapsulation in a slightly bent configuration. Panels reproduced with permission from (A) Springer Nature Ltd; (B) Springer Nature Ltd; (C) Elon Musk, Neuralink, CC-BY-ND-4.0; (D) Springer Nature Ltd; (E) Frontiers, CC-BY-3.0; (F) Elon Musk, Neuralink, CC-BY-ND-4.0; (G) Elsevier; (H) Frontiers, CC-BY-3.0; (I) Elsevier; (J) PNAS.

Overall, the sputtering method can perform wafer-level online modification on high-density neural recording sites with high efficiency, but the impedance performance of the modified recording sites varies depending on the sputtering parameters and the positions on the wafer.72 Therefore, there is ample room for optimization in achieving the high consistency of impedance performance of high-density microelectrodes to improve the yield rate of a neural electrode array.

The aim of developing high-density electrodes is to ensure their durability while implanted in the body for a long time. However, the complex and dynamic nature of the brain's liquid physiological environment poses a significant challenge to maintain the stability of the electrode array's performance. This challenge is evident in the brain's heterogeneous and foreign body response (FBR) to the implantation of extracorporeal devices. Over time, this response reduces the effectiveness of the electrode-neural interface.73 The following sections will discuss the impact of rejection on the neural signal yield rate of high-density recording arrays, considering acute and chronic reactions. Acute injury is mainly due to mechanical damage from electrode implantation. As the implanted electrode connects to the predetermined brain area, it can shift and damage the vascular system, blood-brain barrier (BBB), cells, and extracellular matrix (ECM). Once the injury occurs, microglia quickly gather in the damaged area to initiate wound healing.74 Researchers have been trying to minimize tissue damage during the implantation of probes by making them smaller and more mechanically flexible. However, as the number of channels and the volume of the implant increase, it becomes more challenging to implant high-density brain electrodes without causing significant damage to the brain tissue. The high-density microneedle electrode array6 and silicon-based CMOS electrodes75 are rigid with implants of high stiffness. Thus, they can be directly implanted into the pia mater without auxiliary tools, as shown in Figure 4D. However, the rigid probe's micro-movement after implantation can cause tissue inflammation and vascular rupture, leading to punctate bleeding. Figure 4E shows the details of punctate bleeding after the acute implantation of a 100-channel rigid electrode into human temporal lobe specimens, sharply reducing the yield rate of neural spikes. The stiffness of the flexible high-density electrodes on the flexible neural probe is insufficient. Therefore, its implantation requires the application of polyethylene glycol (PEG) wrapping to harden the flexible probe76 or implant the high-density flexible probes with the implantation robot, as shown in Figure 4F. However, the fracture of flexible probes during implantation and the interweaving and overlapping of high-density recording sites caused by PEG dissolution will decrease the effective channel number of high-density flexible electrodes and further reduce the yield rate of the neural recording array.

An analysis of the chronic rejection response in the brain reveals that using high-density rigid probes in vivo for an extended period can result in mechanical mismatches with brain tissue. This problem can cause the probe structure to move slightly due to vascular pulsation or respiration, leading to cuts in brain tissue and prolonged damage. As a result, reliable tracking of individual neurons for several days or longer becomes difficult.77 Long-term sustained brain tissue damage can result in the formation of dense glial scars in the affected area. These scars, which can be several hundred micrometers thick, are formed by activated microglia and astrocytes, as shown in Figure 4G,78 leading to severe degradation of the electrical coupling between implanted electrodes and neurons, resulting in a rapid decrease in the signal-to-noise ratio of neural signals and the number of neurons capable of recording. In addition, the cerebrospinal fluid in the brain contains a high amount of water vapor and a complex mix of biomolecules, such as inorganic salts, biological enzymes, and reactive oxygen species (ROS) factors.79 Due to the prolonged exposure to this complex environment, the polymer insulation layer of the metal microwire electrode implanted in the body is prone to corrosion in Figure 4H.80 Similarly, the silicon-based Michigan-style probe also encounters this issue,78 as illustrated by the white arrow mark in Figure 4I. The high-density flexible neural recording array has high biocompatibility, adapts to brain tissue movement, and does not cause obvious glial cell encapsulation. However, the brain contains a large amount of water vapor, which can cause problems for flexible polyimide substrates due to their high moisture absorption rate. When the substrate absorbs the water vapor in the cerebrospinal fluid, it can lead to delamination and cracking. The water vapor can also cause cross-connections between nearby recording sites, degrading the performance of the insulation layer in flexible high-density neural recording arrays and resulting in microelectrode failure. This damage sharply reduces the neuron signal yield rate of the high-density flexible recording array.

In terms of improving the resistance of the neural electrode insulation layer to water vapor erosion, Hui Fang and colleagues utilized a transfer thermal oxidation technique to cultivate a second oxide layer, which serves as a biological protective layer structure for flexible electronic devices, as shown in Figure 4J. They conducted accelerated aging experiments in phosphate buffer saline (PBS) solution for 70 years to confirm the effectiveness of this protective layer structure and its validity period.81 On this basis, Enming Song et al. further deposited ultra-thin hafnium dioxide (HfO2) thin films on thermally oxidized silica layers, achieving a double-layer hybrid biological encapsulation. This double-layer barrier can simultaneously hinder the diffusion movement of water vapor and ions within biological devices, further improving the service life of biological electronic devices.82 While organic thin films have functioned as protective layers in flexible bioelectronic devices,83 we need more research to determine how to integrate these thin films into high-density neural electrodes. Additionally, further testing is necessary to confirm their functionality inside the brain. This work will significantly improve the long-term neural signal yield rate of high-density neural electrodes in vivo.

Table 1 summarizes the technical details and performance of the high-density neural recording electrode reported previously.

| Year, Ref | Electrode | Pad size | Pitch size | Channel | Bonding method | Package substrate | Substrate size | In vivo test | Spikes yield rate |

|---|---|---|---|---|---|---|---|---|---|

| 20206 | Microwire bundle | \ | 40 μm | 8640 | Compressing | Xenics Cheetah camera chip (CMOS chip) | Diameter about 5 mm | Acute in awake moving mice | 41.1% (67/163) |

| 20207 | Microwire cores (90%Pt/10%Ir) | 40 × 40 μm2 | 50 μm | 65,536 | Pressed onto the chip | CMOS sensor in the Argo system | 14.5 × 16 mm2 | Rat cortical recordings | 791 single units in 1300 microwires |

| 201612 | 3-D silicon probe | 200 μm | 256 assemble to 1024 | Chip bonding with ACF | Flexible cables & PCB | \ | Awake mice | \ | |

| 201524 | Silicon probe (Ti, Au) | 250 × 125 μm2 | 250 μm | 64/128/256/1000 | Wire bonding | PCB | \ | Cortex of an anesthetized mouse | \ |

| 202213 | Flexible neural probe | ∼5600 μm2 (for LNA) | 75 µm | 256 | Chip bonding with ACF | AFE integrated circuit chip | 2.88 × 1.43 mm2 | CA1 region of rat | Local field potential (LFP) signals (210/25) |

| 2022 61 | Flexible neural probe | 280 × 220 μm2 | 380 μm (horizontal); 320 μm (vertical) | 1024 | Gold-ball bonding (80 μm) | PCB | 11.8 × 10 mm2 | \ | \ |

| 201960 | Parylene flexible neural probe | 200 × 140 μm2 | 100 µm | \ | Wedge bonding, polymer-ultrasonic-on-bump (PUB) | ASIC chip | \ | \ | \ |

| 202265 | PtNRGrids | \ | 150 μm | 1024/2048 | Bonding by silver epoxy | LGA- (PCB) | \ | Acute mapping sensory/motor regions | \ |

| 200 μm | |||||||||

| 20229 | Ultraflexible nanoelectronic thread electrodes (NETs) | \ | 500 μm | 2304 (18–128 channel NETs) | Ball grid array (BGA) flip chip | Flexible printed circuits (FPCs) | \ | Six weeks post-implantation in mouse visual cortex | 1355 units from 1036 channels |

| 201910 | Ultra-fine polymer probes | \ | \ | 3072 | Flip-chip bonding | PCB | 23 × 18.5 mm2 | Male long-evans rats | Average spiking yield of 45.60%; maximum of 70% |

| 1536 | |||||||||

| 202353 | Mechanically robust ultraflexible, 1 μm thin electrode array | \ | \ | 128 channels in each module | Ball grid array (BGA) flip chip | Flexible printed circuits (FPCs) | 42 mm in length | Up to 240 days in nonhuman primates | 2913 units from 1065 functional recording channels |

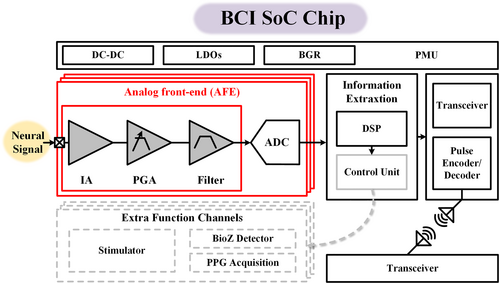

3 HIGH-DENSITY NEURAL RECORDING CHIPS

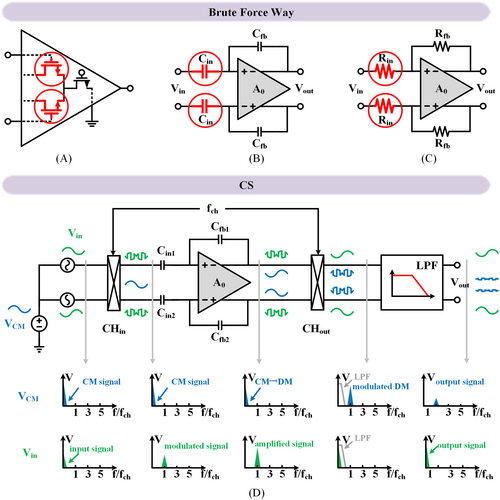

To achieve cellular-scale resolution, the analog frontend circuits (AFEs) of the system-on-chip (SoC), as shown in Figure 5, should be miniaturized to match the massive recording channels with micrometer-scale electrode sites. Under such a restricted area constraint, the AFE also needs to be designed with satisfactory electrical performance, for example, low noise, high common-mode rejection ratio (CMRR), and high input impedance to obtain clear neural potentials since the amplitude of neural potentials can be as tiny as tens of μV. Without design innovation, the electrical performance of AFE can be merely maintained in a brute-force manner, that is, at the cost of power consumption and silicon area. Unfortunately, unlimited size or device space is impossible, which inspires many area-efficient, energy-efficient, or both design techniques along the trajectory of reported BCI readout chips from a few channels to state-of-the-art massive designs over 1000 channels. This part reviews such techniques from both circuits and architecture-level design innovations.

Block diagram of a typical BCI SoC.

3.1 Circuits-level techniques innovations for massive recording

Due to the rapid development of BCI AFE chips over the past decades, many innovative circuit techniques deserve a detailed review. This section summarizes several representatives of those reported innovations to achieve low input referred noise (IRN), high CMRR, and high input impedance of the AFE chips, providing possible insights into the massive AFE channels.

3.1.1 Noise suppression

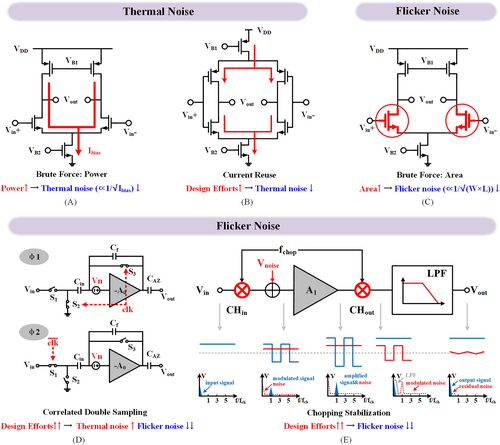

The digitalized neural recording is the superposition of the neural potential and the noise from both electrodes and AFEs. Thus, the IRN of the AFE needs to be less than ten μVrms for precision hundreds of μV neural recordings.84 One can achieve this result via brute force by simply increasing the power consumption85, 86 and silicon area87 to suppress the thermal and flicker noise of the AFE, respectively.

Theoretically, thermal noise is inversely proportional to the square root of the current flowing through the input transistors of the amplifier. Flicker noise depends on the size of the input transistors. Figure 6A presents a typical amplifier fabricated in a CMOS process. The current, Ibias, must be increased by 4× to reduce its thermal noise by half. Thomas Desel et al. reported that 32.5 μA is necessary to obtain 1.39 μVrms IRN.88 However, 485 μA current dissipates to achieve 0.86 μVrms IRN.89 Thus, the power cost is nontrivial by simply increasing current for low thermal noise even for a single amplifier, not to mention the rapidly increased recording channels where thousands of amplifiers could be required.

Noise suppression (A) brute force: high power consumption, (B) current reuse op-amp, (C) brute force: large input pair, (D) correlated double sampling (CDS), (E) chopping stabilization (CS).

Researchers can mitigate thermal noise by reusing the input current via a complementary input transistor in Figure 6B.90 In this way, the input takes twice the usage of the bias current and offers 2× power efficiency. One can leverage such a scheme to obtain 1.01 μVrms IRN across 180 Hz bandwidth with merely 370 nA current.91 This technique has been widely adopted in the state-of-the-art.90, 91

Transistor flicker noise (also known as 1/f noise) dominates the noise spectrum below several tens of kHz due to its slowly but prominently varied amplitude. Thus, flicker noise optimization deserves more attention to maintain the IRN under the expected level for a neural recording. This result is because neural signals such as local field potential (LFP), electrocorticography (ECoG) and action potential (AP) are far below 10 kHz. As shown in Figure 6C, at the cost of 0.33 mm2 silicon area, the IRN of the AFE is lowered to 3 μVrms.87 Then, it is further minimized to 1.46 μVrms at 6.32 mm2 area.92 Although enlarging the silicon area is simple and effective for BCI applications without the necessity of massive recording channels, it becomes unaffordable when the number of recording channels increases. For example, the silicon area will be 6320 mm2 for 1000 AFE channels without any digitalization if adopting the brute force approach.92

To minimize flicker noise with restricted silicon area, researchers with many dynamic circuit design techniques, such as correlated double sampling (CDS) and chopper-stabilization (CS) were developed. As seen in Figure 6D, CDS mitigates flicker noise via two correlated phases. During phase φ1, both S2 and S3 are closed to store the noise and the offset of the amplifier A0 with reversed polarity on Cin. Then, the stored noise and offset are supersized on the input to cancel the amplifier noise and offset. One can implement the two phases by two half cycles of a clock. If both phases are short enough (fast enough clock frequency), then the noise stored in φ1 can be taken the same as the noise in φ2 but with reverse polarity. Such a condition is taken as correlated. This method significantly suppresses the amplifier noise and offset because of the correlated subtraction. For instance, it can attenuate flicker noise from 1 μV/√Hz82 to <150 nV/√Hz at 1 Hz, taking merely 1.48 mm2 silicon area.93 However, CDS would fold the thermal noise back into the signal band, resulting in a 2× price of thermal noise, showing its noise limitation.94

Unlike CDS, CS leverages the modulation mechanism by separating the signal and amplifier noise in the frequency domain without the concern of thermal noise foldback. As shown in Figure 6E, input is first upmodulated to the spectrum centered at the chopping frequency, fchop, via CHin. After traveling through the analog front-end amplifier A1, the amplifier flicker noise is added to the low-frequency domain, denoted by an input noise Vnoise. Thus, after the second chopper (CHout), the flicker noise is upmodulated to fchop while the signal is demodulated back. Consequently, a lowpass filter (LPF) can easily filter the flicker noise. One can achieve a noise floor around 100 nV/√Hz (0.98 μVrms IRN) at 1 μA current consumption and 1.7 mm2 chip area.95 A recent design, drawing more current, that is, 2.5 μA, effectively suppressed the noise to 40 nV/√Hz (0.516 μVrms) within a compact area of 0.3 mm2.96 In this view, Rémi Dekimpe et al. reported the chopping stabilized capacitive coupled instrument amplifier (CS-CCIA) to achieve 750 nVrms IRN at 1.17 μA current and 0.024 mm2 area,97 showing excited noise effective factor (NEF) and area efficiency. Recently, a group chopping approach was devised for an 8-channel AFE, obtaining a remarkable 420 nVrms IRN at a minimum cost of 2.4 μW power and 0.017 mm2 area.98

Table 2 compares the noise performance of the representative designs with associated design techniques and the area and power costs. The brute force approach requires a large silicon area or high power consumption to obtain the expected noise performance. While CDS lowers both area and power, the noise spectrum barely lowered more than 130 nV/√Hz. Current reuse lowers the noise to less than 100 nV/√Hz but still requires a sizable area. CS can minimize the flicker noise and thus the total input referred noise at complex design efforts without the thermal noise folding issue yet the necessity of a large silicon area, which is promising for high-density recordings.

| Year | 201687 | 200589 | 201193 | 201591 | 202297 | 202298 |

|---|---|---|---|---|---|---|

| Noise suppression tech. | (a) | (a) | (d) | (c) | (e) | (e) |

| Brute force: Area | Brute force: Power | CDS | Current reuse | CS | CS | |

| Process | 0.13 μm | 0.5 μm | 0.5 μm | 0.18 μm | 28 nm | 0.18 μm |

| Current (μA) | 1.19 | 485 | 480 | 0.37 | 1.17 | 4.2a |

| Noise (μVrms) | 3.06 | 0.86 | 1.59 a | 1.01 | 0.75 | 0.42 |

| Integrated band/Hz | 0.5–150 | 0.3–150 | 0.5–150 | 0.7–182 | 1–100 | 0.1–220 |

| Area (mm2) | 3.75 | 4.81 | 1.48 | 1.6 | 0.024 | 0.017 |

- a Estimated value from the reported contents.

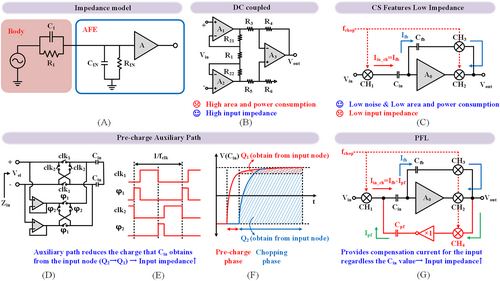

With chopping, input impedance deterioration is inevitable if it does not incorporate a boosting technique. This result is from the alternating connection of the input capacitance at the chopping frequency. For 10 pF input capacitance and 100 kHz chopping frequency, the input impedance would decrease to 1 MΩ, which challenges the recording quality due to the severe potential divider effect. For 100 kΩ electrode impedance, the recording would experience a 0.83 dB signal-to-noise ratio (SNR) loss under 1 MΩ input impedance. Thus, chopping necessitates effective input impedance boosting techniques.

3.1.2 Input impedance boosting

As shown in Figure 7A, high input impedance enhances the acquisition of neural signals and mitigates the electrode impedance deterioration during long-term recording.99 Unlike DC-coupled AFE,100 which achieves inherent high input impedance (IIP), CS AFE features the lowest area and power cost at the minimum noise but may lead to sub-MΩ IIP. Thus, researchers have developed many IIP-boosting techniques for CS AFE. Charge transfer between the differential input capacitance due to chopping is the primary cause of IIP deterioration. Adding an auxiliary path to pre-charge the input capacitance to a level required for the following chopping can reduce the charge transfer during chopping, boosting the IIP from 21 MΩ to 1.6 GΩ.101 The area and power cost of such an auxiliary path are trivial. However, it also injects noise into the input during pre-charge, resulting in 1.8 μVrms IRN, increased by 2.5× compared to the design without an auxiliary path.100

Input impedance boosting (A) neural recording impedance model, (B) DC coupled three op-amp IA, (C) CS topology features low impedance, (D) pre-charge auxiliary topology, (E) timing diagram of pre-charge, (F) comparison of charges obtained from the input node, (G) positive feedback loop (PFL) topology.

A positive feedback loop (PFL) can boost the input impedance over 80 MΩ (Figure 7G) as it provides compensation current for the input regardless of the input capacitance value.102 With the help of self-calibration, PFL allows for an impressive 2.67 GΩ input impedance with 0.405 mm2 silicon area and 2.8 μA current cost.103 Leveraging a dual feedback loop PFL in combination with self-calibration enhances the input impedance to 15 GΩ@10 Hz at 0.75 mm2 area and 3.63 μA current.104 Considering that the input impedance of implantable high-density electrodes approximates 100 kΩ@10 kHz,105, 106 IIP exceeds 10 MΩ@10 kHz and is sufficient to prevent over 1% signal attenuation. However, the electrode impedance might reach 1 MΩ during a long recording, necessitating a reliable input impedance boosting technique. PFL with on-chip one-time calibration is promising because of its minimal area and power cost while free of excessive noise injection.

3.1.3 Channel crosstalk

Common-mode disturbances, power fluctuations, and other voltage ripples arising from clock switching, channel switching, chopping, and sampling can induce severe channel crosstalk, leading to the inability of accurate multichannel recording. As a result, it is essential to design AFE with a sufficient common-mode rejection ratio (CMRR) and power supply rejection ratio (PSRR) to minimize possible interferences, ripples, and thus crosstalk.107, 108 The CMRR of the AFE should exceed 60 dB to accommodate a 1 V common-mode (CM) variation of no more than 1 mV expected variation on the recording.108 Thus, to attain 10 μV recording distortion, 100 dB CMRR might be necessary if 1 V CM variation occurs. Similarly, it requires a 70 dB PSRR to translate the 100 mV powerline ripples to no more than a 5 μVrms neural signal.109

A fully differential amplifier, as shown in Figure 8A, can achieve a CMRR of around 76 dB with a large transistor size, consuming 0.405 mm2 core area.110 Employing a large input capacitor or resistor (Figure 8B,C) can achieve a CMRR of 90 dB, with the required silicon area enlarged to 2.28 mm2.111 However, such excessively sizable passive devices on the chip for massive channels are impractical. One can also enhance CMRR by utilizing a common-mode signal extraction path at the AFE input node, achieving CMRR over 130 dB within a compact area of 0.227 mm2.112 However, this improvement comes at 3.14 μVrms noise due to the absence of a noise suppression technique. CS is beneficial in flicker noise suppression and CMRR enhancement.113 As shown in Figure 8D, passing through a fully differential amplifier, the input common-mode is translated into differential mode due to the mismatch of the ratio capacitors. This common-mode signal cannot be modulated by CHin and then translated into low-frequency differential output after A0. The low-frequency differential is then up-modulated by CHout while the signal is demodulated and thus separated with the differential interferences induced by CM variation, achieving 120 dB CMRR and 516 nVrms IRN, all within 0.3 mm2 chip area.96

CMRR Enhancement (A) large transistor size, (B) large input capacitor, (C) large input resistor and (D) chopping stabilization.

Adopting an AFE with high PSRR cleans the recording ripples due to power line variations while avoiding the usage of the power-inefficient LDO. It thereby reduces the total system power. A conventional neural amplifier can achieve over 70 dB PSRR.114, 115 Replica biasing effectively boosts the PSRR of the neural amplifier to 110 dB at the cost of 0.39 μW power and 0.04 mm2 silicon area.116 A differentially regulated rejection-ratio enhancement scheme by Sehwan Lee et al. enhanced the PSRR over 100 dB, consuming 3.23 μW power and 0.075 mm2 area.109

In short, massive channel neural recording poses challenges to electrical performances, such as noise, IIP, crosstalk, and many more, with restricted power and area constraints. Many design techniques are developed at the circuit level, for example, current reuse, CDS, CS, PFL, and replica biasing to replace the brute force manner, providing an insight chip-level design cornerstone for massive recording applications.

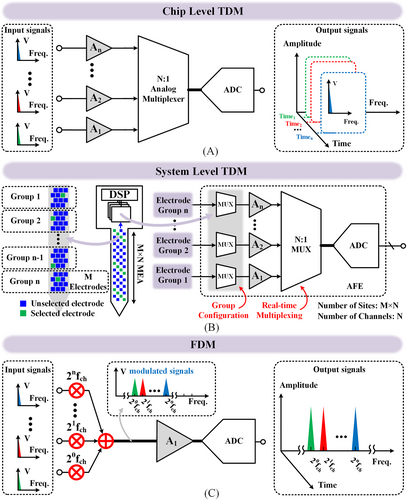

3.2 Architecture-level techniques for massive recording

The human brain contains over 80 billion neurons. A state-of-the-art massive neural recording contains only several thousand channels, revealing a vast gap toward full-brain cellular-scale recording resolution. This goal is limited by silicon area, power consumption, and fabrication yield.117 Researchers specifically develop many emerging circuits and architecture design techniques for a massive channel recording that offer higher area density, better energy efficiency, and higher yield.

One such design involves 16-channel recording.118 Time domain multiplexing (TDM) is utilized for a density of 0.077 mm2/channel. Notably, a miniaturized, high-density TDM-based neural recording interface shows 0.0161 mm2/channel for 256 total recording channels.13 As shown in Figure 9A, TDM enables the ADC sharing and thus trading the ADC speed and power for area density. Most BCI chips investigated with more than hundreds of channels employed this technique.105, 106, 119, 120 This approach allows for a remarkable reduction in the recording area, with designs achieving as small as 0.0161 mm2/channel. Such compact designs enable the realization of BCI chips with thousands of channels. Even a chip containing 1024 channels can maintain the silicon area within 20 mm2.120

Architecture-level chip design techniques. (A) Chip level time division multiplexing (TDM), (B) system level TDM and (C) frequency division multiplexing (FDM).

Chip-level density improvement benefits manufacturing yields and thus provides a lower cost. For a conventional 1000-channel recording chip occupying 220 mm2 silicon area, 268 dies can be obtained on a 12-inch wafer. The number of dies significantly increases to 624 for a TDM-based recording chip with over 1000 channels (<100 mm2). The reduced area/die improves the defect-limited yield by over 10%.121 This change almost triples the number of usable dies obtained on a wafer, offering an over 66% cost reduction.

However, concerns still exist at the chip-level TDM-based implementations. Trading power for area burdens the power supply unit of the recording system, impeding the system-level miniaturization. Limited by the power consumption, the (PCB) size is expanded to a diameter of 3.5 cm for thermal dissipation,106 not to mention the required battery, cables, etc., making it unable to be used on freely moving animals.

This result causes two further issues. On the one hand, mainstream bio-medical devices typically include batteries with a capacity of only a few hundred mAh, making it challenging for long-term usage, even for several weeks. On the other hand, implantable multi-channel recording chips must deal with thermal heating. Assuming a heat transfer coefficient of 1000 W/(m2·°C)122 between the chip and brain tissue, a 100 mm2 sized chip consuming 690 mW106 power will cause a temperature rise of 6.9°C, which is unacceptable in fundamental neuroscience research, translational, or clinical medical usage.

Researchers can also apply TDM at the system level. Figure 9B depicts over 10,000 microelectrode sites connected to 1000 recording channels.114 This configuration enables high resolution while maintaining a small chip area and low power consumption by TDM tens of electrodes to one active AFE channel. For instance, a BCI system featuring 19,584 recording sites is obtained via a recording chip with only 246 active chip channels. This chip consumes a total power of 9 mW and takes a silicon area of 54 mm2.15 According to a recent report from Jelena Dragas et al.,105 a tool is designed with 59,760 recording sites associated with a chip with 2048 active AFEs. The chip occupies 106.8 mm2 area with 86 mW power.

Whether chip-level or system-level TDM, ADC sharing maintains the extended spatial resolution at the sacrifice of temporal resolution, the cost of power consumption, and, thus, device size. System-level TDM enables much higher recording sites, but it can record only part of them simultaneously after the site selection. Researchers are still searching for a strategy to implement as many effective AFE channels as possible for simultaneously massive recording at a reasonable silicon area and power consumption.

Frequency division multiplexing (FDM) is a valuable multi-channel technique that further enhances the efficiency of area and power consumption via ADC and amplifier sharing. As shown in Figure 9C, each AFE directly connects to several recording sites, each modulated by a unique orthogonal frequency. Then, multiple sites simultaneously pass through one AFE channel in the time domain via a frequency domain multiplexing. Then, the recorded signals from several sites are digitally processed via filter banks to recover the modulated signals. Compared to analog-dominated AFEs, the extra digital processing is process-scaling friendly, and its cost is negligible. A representative FDM design123 achieves 0.019 mm2/channel density and 1.64 μA/channel energy efficiency, showing a 75% improvement over a chip-level TDM design.118

Analog components such as amplifiers, resistors, and capacitors dominate the AFEs in both TDM and FDM topologies. Such analog design is not friendly to process scaling. For example, the design in 28 nm takes even more silicon area and higher power consumption than the design in a 180 nm process, as shown by the last two columns of Table 2.

In addition, typical neural recording AFEs usually apply low-power neural amplifiers and successive approximation ADCs (SAR ADCs), digitizing the signal in a power-efficient manner.124

Is it possible to directly digitalize the neural signal without the power-hungry or area-inefficient neural amplifiers (i.e., the AFEs) via only an ADC? Recent works, such as ADC-only front-ends reported by Xiaolin Yang et al.125 and Daniel De Dorigo et al.,45 demonstrate such concepts by leveraging Continuous-time delta-sigma modulators (CT-DSM) analog-to-digital conversion techniques.125-127

CT-DSM can replace the classic neural interface of AFE and ADC because it achieves high DR and low quantization noise due to the oversampling principle while preserving the antialiasing feature. For example, Xiaolin Yang et al. reported that an ADC-only front-end achieved 0.98 μVrms and 108 dB DR in 41 μA power consumption and 0.48 mm2 area per channel.125

Although the work of Xiaolin Yang et al. is good, two concerns exist limiting the practical application of conventional DSM-based direct digitalization circuits. First, analog components still dominate this architecture, such as high linearity DAC,45 low noise amplifier,126 and an integrator,127 which are neither friendly to scaled processes nor supply voltage. Secondly, the tens of MΩ level input impedance of this architecture requires a high driving capability of the signal source, which further limits its application scenario.

Voltage-controlled oscillator (VCO) based direct digitalization technique translates voltage signals into the time domain via digital standard cells, showing its superiority, especially in the advanced fabrication process node.128-133 Such direct digitization architecture results in greater area and energy efficiency because of its compatibility with process scaling.

Wenlong Jiang et al. first reported that the VCO-based direct digitalization (VCO-DD) architecture achieves area and energy efficiency of 0.135 mm2/channel and 11.3 μA/channel, respectively.129 With a shift-register-based optimization, they further reduce to 0.12 mm2/channel and 10 μA/channel.130 It is then optimized to 0.08 mm2/channel and 3.41 μA/channel, competing with a TDM architecture.131 A state-of-the-art VCO-DD can easily achieve 0.01 mm2/channel and 1 μA/channel.132 We expect to obtain a BCI with 10,000 recording channels, consuming only 9.9 mW power meanwhile occupying just 110 mm2 silicon area via the VCO-DD technique. Table 3 compares representative works using TDM, FDM, and VCO. It shows that promising area and energy-efficient chip design techniques are emerging for massive neural recordings with acceptable noise performance.

| Year | Architecture | Process | Recording sites | Recording channels | Power (μW)/channel | Area (mm2)/channel |

|---|---|---|---|---|---|---|

| 202213 | Chip level TDM | 0.18 μm | 256 | 256 | 51.92a | 0.0161b |

| 2021120 | Chip level TDM | 65 nm | 1024 | 1024 | 24.08 | 0.02b |

| 202115 | System level TDM | 0.18 μm | 19,584 | 246 | 39.1 | 0.1939a |

| 2020123 | FDM | 0.18 μm | 15 | 15 | 1.97 | 0.019 |

| 202145 | CT-DSM | 0.18 μm | 8 | 8 | 14.94 | 0.00462 |

| 2018126 | CT-DSM | 0.18 μm | 144 | 144 | 46.29 | 0.00049 |

| 2021127 | CT&DT-DSM | 55 nm | 16 | 16 | 61.2 | 0.0077 |

| 2023128 | VCO | 0.18 μm | 20 | 20 | 4.4 | 0.0013 |

| 2021132 | VCO | 0.13 μm | 16 | 16 | 0.99 | 0.011 |

| 2019133 | VCO | 40 nm | 32 | 32 | 8.2 | 0.12 b |

- a Estimated value from the reported results.

- b Per channel area = full area of die/number of channels.

4 CONCLUSIONS AND PERSPECTIVE

One of the biggest mysteries in science and engineering today is how the brain circuits and neural networks function. Neuroelectrophysiology plays a vital role in analyzing the function of neural circuits.118 The unprecedented need for large-scale neural signal recordings places higher demands on implantable devices. Undoubtedly, implantable electrodes and chips are integral components of this field and are intricately interconnected.134 The microelectrode impedance of implantable electrodes, parasitic capacitance of high-density slender wires, and signal crosstalk between adjacent wires all demand superior performance from implantable chips. High-density, high-performance implantable recording chips require the size of implantable electrodes to be as small as possible. This feature enables seamless integration with hundreds or even tens of thousands of channel recording chips. Low noise and low impedance electrodes are also critical for the recording chips to acquire high-quality signals. The co-optimization of the electrode and chip enables an excellent BCI system.

This review discusses exciting advances in high-density implantable neural electrodes and chips. On the one hand, the fabrication, formation, bonding strategy, and in vivo performance optimization of high-density neural electrodes are reviewed by typical works. On the other hand, we discussed chip design techniques at both circuit and architecture levels in achieving lower power consumption, smaller areas, and better performance for high-density, numerous recording channels. Although researchers have made significant breakthroughs in recent years, the current density of synchronous recording neurons is far from what is necessary for neuroscience research.

Researchers must fulfill the fast demand for full-brain cellular-scale spatiotemporal resolution by addressing many other challenges, including but not limited to the following: (1) the miniaturized and high-affinity brain tissue of electrodes, including the application of new materials, new structures, and new processes in electrode formation to achieve a yield rate of neural signal with little intrusion damage; (2) vast volumes of on-chip and off-chip data processing and transmission associated with the ever increased recording channels, including the utilization of new architectures and advanced processes to optimize the area and power efficiency of the recording chips, and the introduction of noise suppression technique to suppress the input referred to as noise for high-quality signal acquisition; (3) the biocompatibility and stable bonding of electrodes and chips: more advanced high-density and highly reliable fan-out schemes, including through-hole substrate connections, feed-through connections, and wafer-level packaging technologies should be widely used in the bonding of electrode and chip; 4) the airtight, miniaturized and reliable packaging of high-density BCI systems: more materials like polychlorotrifluoroethylene with high tissue affinity and strong corrosion resistance should be developed and widely used in the packaging of high-density systems.

A conflux of emerging technological breakthroughs and discoveries from material science, mechanical engineering, biomedicine, artificial intelligence, and many other disciplines would continuously inspire astonishing cutting-edge high spatiotemporal neural recording tools. With joint efforts from multidisciplinary researchers, the density and the functionalities, modalities, and biocompatibilities of the BCI tools will inevitably improve unexpectedly rapidly. Following such a pace, new challenges, but more importantly, new opportunities are ahead.

AUTHOR CONTRIBUTIONS

Longchun Wang: Conceptualization, investigation, visualization, writing-original draft, writing-review & editing. Yanxing Suo: Investigation, visualization, writing-original draft. Jiahao Wang: Investigation, visualization, writing-original draft. Xuanqi Wang: Data curation and investigation. Kai Xue: Validation; resources. Jingjing An: Investigation; Xun Sun: Investigation. Qinyu Chen: Writing-review & editing. Deepu John: Writing-review & editing. Yang Zhao: Conceptualization, funding acquisition; investigation; methodology; writing-review & editing. Bowen Ji: Conceptualization, funding acquisition, methodology, project administration; resources; supervision; writing-review & editing. Jingquan Liu: Funding acquisition, visualization, project administration.

ACKNOWLEDGMENTS

This work acknowledges the support received from the Science and Technology Innovation 2030-Major Project (2022ZD0208600, 2022ZD0208601, 2022ZD0208500), the National Natural Science Foundation of China (Grant No. 62104145, 62204204, 62304135, 42127807-03), Shanghai Sailing Program (21YF1451000), the National Key R&D Program of China (2022YFB4400800) China Postdoctoral Science Foundation (2023M732197). We acknowledge the technical support from Neuracle Medical Technology (Shanghai) Co., Ltd; the Center for Advanced Electronic Materials and Devices (AEMD) of Shanghai Jiao Tong University.

CONFLICT OF INTEREST STATEMENT

Xun Sun is an employee in Institute of Guizhou Aerospace Measuring and Testing Technology, but has no potential relevant financial or non-financial interests to disclose. The other authors declare that they have no conflicts of interest.

ETHICS STATEMENT

Ethics approval was not needed in this study.

Open Research

DATA AVAILABILITY STATEMENT

All data used to support the findings of this study are included in the article. Raw data used to generate the figures are available from the corresponding author upon request.