Verification of Mixed-Signal Systems with Affine Arithmetic Assertions

Abstract

Embedded systems include an increasing share of analog/mixed-signal components that are tightly interwoven with functionality of digital HW/SW systems. A challenge for verification is that even small deviations in analog components can lead to significant changes in system properties. In this paper we propose the combination of range-based, semisymbolic simulation with assertion checking. We show that this approach combines advantages, but as well some limitations, of multirun simulations with formal techniques. The efficiency of the proposed method is demonstrated by several examples.

1. Introduction

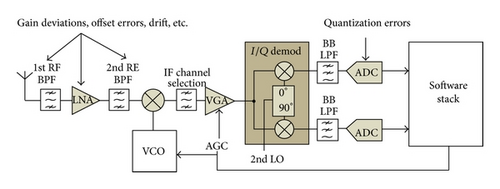

Analog/mixed-signal (AMS) systems are a crucial part of today’s embedded systems. Typical AMS components such as sensors, transceivers, and signal conditioning enable interaction of embedded HW/SW systems with its physical environment. In today’s embedded systems, the functionality of the analog components is tightly interwoven with the digital HW/SW system. A particular challenge of AMS systems is that parameters cannot be assumed to be fixed to a deterministic value like in a digital system.

Behavior of AMS systems cannot be assumed to be fixed for the following reasons: variations of parameters due to variations in the manufacturing process, but as well during operation (e.g., different temperatures, aging, and supply voltage) introduce deviations compared to an ideal reference. (Modeling) uncertainties are introduced by the fact that all models represent more or less accurate abstractions of physical reality. No model can be assumed to be absolutely accurate. Furthermore, computation with fixed-point arithmetic in the digital domain can contribute significantly to deviation from expected ideal behavior (rounding errors, quantization). In the following we refer to such deviations of a simulation run from possible real behavior in general as “deviations.”

- (i)

how can we guarantee some system properties, for example, for safety relevant systems?

- (ii)

can we get information from the analysis that assists us in design and debug, such as counter examples?

- (1)

assertions specify required properties of a system;

- (2)

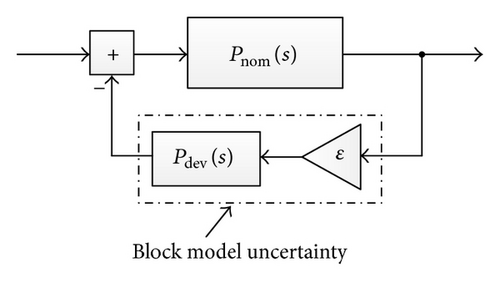

in an overall system model, deviations and variations are represented by symbols that capture size and correlations of the deviations, variations, respectively;

- (3)

for verification of “worst case” behavior, a range-based simulation using Affine Arithmetic shows that for given ranges of inputs and deviations the required properties are valid, and that no “forbidden state” is reached.

We mostly focus on level of block diagrams, but the methodology is as well applicable on circuit simulation. We implemented it based on SystemC and its AMS extensions. Section 2 gives a review of state of the art and related work. In Section 3 Affine Arithmetic is described, and some modeling examples are given. Section 4 describes semisymbolic simulation and the verification method proposed in this work. The applicability of the verification technology is demonstrated by examples given in Section 5. Section 6 concludes the paper and identifies future work.

2. State of Art and Related Work

When verifying AMS systems with parameter deviations, application of multirun simulation techniques (Monte-Carlo, worst-case analysis) can be considered as state-of-the art. Monte Carlo simulation [1] is a statistical technique. However, statistical techniques do not provide dependable “worst case” results. While the number of simulation runs can be reduced by importance sampling [2], the number of simulation runs required may still be prohibitive for analysis of complex systems. Corner case analysis [3] is a more appropriate means for finding worst case performances of AMS systems. Unfortunately, the number of simulation runs grows exponentially with the number of parameters considered. However, even if all corner cases are considered, the dependability of the result cannot be guaranteed since corner cases are not necessarily worst cases. Design of Experiments [4] allows reducing the number of simulation runs significantly and finding worst case performances more accurately.

Even with high number of simulation runs, there is no guarantee that worst case performances are found. A drawback of multi-run simulation methods is that the dependable operation of AMS systems cannot be guaranteed under all circumstances. For safety-critical systems, for example, in aviation or automotive systems this is a major drawback and motivation for further research.

In order to find counter examples, rapidly exploring random trees [5, 6] and robust test case generation have been proposed in [7–9]. Further, the simulation techniques proposed in [10, 11] guarantee that a system is “safe” if a set of trajectories lie within certain regions defined by previously found conditions. In contrast to these approaches the techniques proposed in [12, 13] compute an overapproximation of the set of states reached by all trajectories. While these methods support debugging and introduce coverage metrics, they are not able to deal with the increased complexity of systems that with deviations and variations. An approach that enables safety verification of hybrid systems with uncertain parameters is the use of barrier certificates proposed in [14]. Those methods can verify if a set of system trajectories crosses a barrier previously defined by a barrier certificate. Finding a proper barrier certificate is not easy and makes this approach difficult for system verification.

To cope with the drawbacks of simulation-based techniques, formal verification methods were proposed. The idea of formal methods is to use the formal checkers which automatically explore all possible states and transitions in the system model to check if the desired output behaviour is met or not. Hence, in contrast to simulation-based methods which can verify only one behaviour (for only one input stimuli) per operation, the formal methods deal with the set of behaviours at a time. Approaches for formal verification were firstly applied on digital systems [15–17], and due to their efficiency they found a good way in industrial applications. Approaches that also cover analog/mixed-signal or hybrid systems are rare and still in infancy.

In [18–20] hybrid systems with linear and nonlinear dynamics are approximated by timed automata in order to simplify their analysis. Reference [21] describes a model checking tool which requires discrete and (for continuous parts) linear system descriptions. For nonlinear continuous behavior, such approximations are too simple. Linear phase-portrait approximation [22] is a general technique, because its approximation does not depend on the order of the differential equation to be approximated. There is no standard method for partitioning the state space, and therefore it seems to be complicated to find proper discrete models for strongly nonlinear models. In [23–25] focus is on nonlinear analog behavior for which discretized models in the state space are used for verification. The efficiency of these approaches seems to be limited to smaller analog systems. With increasing complexity, the number of states in the discretized model grows which leads to the state explosion problem and high run time of verification algorithms applied on this model.

Due to limitation of formal methods for analog/continuous systems to small systems, simulation-based techniques are still the only way for verification of more complex analog/continuous and AMS systems. To formalize verification of AMS systems, assertions that describe typical properties of analog systems are the focus of recent research. In [26] mixed-signal assertions (MSA) were proposed to check properties of mixed-signal systems during simulation. These assertions were implemented in a separate SCAC (SystemC AMS Temporal Checker) library. This library is easily integrated in SystemC AMS simulation environment, due to its C++ based nature. In contrast to this approach, [27] features AMT, an offline tool for monitoring temporal properties of mixed-signal systems for verification. Both verification methodologies simulate and evaluate a nominal system model without taking into account any deviations caused by variations in design process.

A particular challenge in design of complex analog/mixed-signal systems is parameter variations. In any physical system, values are not implemented in an accurate way and change in a partially unpredictable way over time (e.g., due to temperature, aging, etc.). Such deviations form an ideal model change system behavior and can potentially cause malfunctions. For conventional simulation, multi-run methods as described in the first paragraph do not provide the result dependability and require a high number of simulation runs to explore the system behaviour while considering process variations. For formal approaches, such issues are still in infancy, because its applicability simply does not yet allow handling complex and heterogeneous systems such as AMS systems.

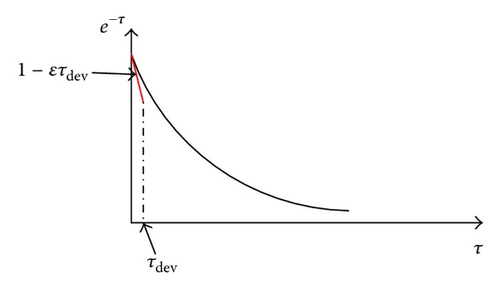

A first approach to cover deviation effects in AMS systems and compute the guaranteed worst case results at the same time was introduced in [28–31]. Deviations are modeled as ranges, superimposed on the nominal system model, and modified during system simulation to obtain the formally guaranteed range-based system quantities. For this purpose, Affine Arithmetic was applied. Using this approach the variations in parameter values are represented with deviated symbols which are traced to the system output. Hence, the contribution of all variations in the system is contained in the system response which simplifies analysis of the system robustness.

In [32] it is proposed that how Affine Arithmetic approach can be used to analyze worst case behavior of electrical circuits. Further, in [33] this methodology found its application in sizing of analog circuits. Using Affine Arithmetic the bounds on the worst case circuit behavior are calculated and the global minimum of sizing problem is determined due to inclusion isotonicity. Beside analog domain, Affine Arithmetic models can also be used in Digital Signal Processing (DSP) applications to represent errors introduced by calculations in floating-point arithmetic [34, 35].

Within this work, semisymbolic simulation based on Affine Arithmetic is combined with the assertion-based technology. Concretely, assertions based on Affine Arithmetic (AAF+A) are introduced to include range-based system quantities and allow specification and automatic verification of typical time and frequency-domain properties of systems considering variations in their parameter values.

- (i)

The desired output behaviour is described with assertion which is embedded into simulation process.

- (ii)

The assertion is verified automatically. In the case where the design requirement is not met the simulation process is stopped reporting the user about the assertion violation.

Table 1 summarizes the advantages and disadvantages of previously described verification techniques.

| Verification techniques | Disadvantages | Advantages |

|---|---|---|

| Multirun simulations | Low verification coverage, no “guarantee” | General applicability |

| Formal methods | State explosion problem, no complex, heterogeneous systems | High verification coverage “guarantee,” counter examples |

| Assertion-based techniques (MSA, AMT tool) | Only nominal behaviour verified, no “guarantee” | Well suited for complex systems, increased coverage |

The verification method proposed in this work copes with the disadvantages of previous verification methods. Concretely, combining the assertion-based technology with semisymbolic simulation, which generates the dependable guaranteed result in which all output values for the considered parameter set are contained, 100% coverage can be obtained.

3. Affine Arithmetic and Its Use for Modeling Deviations

3.1. Affine Arithmetic

Affine Arithmetic (AA) is a range arithmetic that overcomes the error explosion problem of Interval Arithmetic (IA) [36]. AA keeps track of correlations between quantities represented as ranges. This in particular enables application for simulation of control systems. A feedback loop, for instance, can be simulated keeping the correlation of identical ranges. A subtraction of related ranges therefore results in a reduced range avoiding the overapproximation inherent to Interval Arithmetic [29].

3.2. Modeling Examples with Affine Arithmetic

In the following we show how to model different deviations. We focus on block-diagram like representations with transfer functions as common in control theory, because this model of computation is generally applicable to a vast set of different domains, including communication systems and electronic circuits. We focus on giving some mathematical background that can be applied in C-language (as in the examples in later sections), but as well, for example, in Matlab/Simulink.

amp amp_(“amp_”, Knom, Kdev).

3.3. Abstraction of Accurate Model with Affine Arithmetic

For verification of accurate system models in the presence of parameter deviations, a high number of simulation runs is required to achieve a sufficient verification coverage. To deal with this drawback “semisymbolic” approach based on Affine Arithmetic is introduced. Using this method an abstract system model is created in which the accurate system behavior is included. Concretely, abstraction of system model gets an overapproximation of accurate models and therefore gives a guaranty that if the abstract model satisfies desired specifications, the accurate model will also meet them.

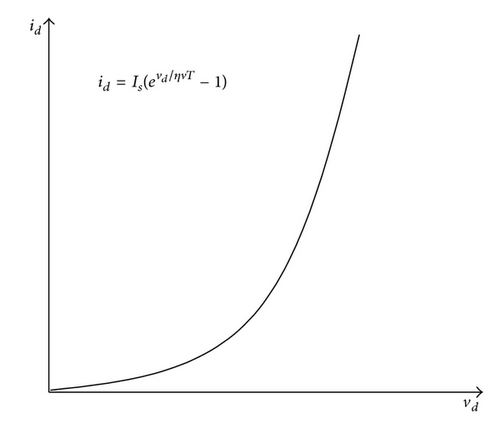

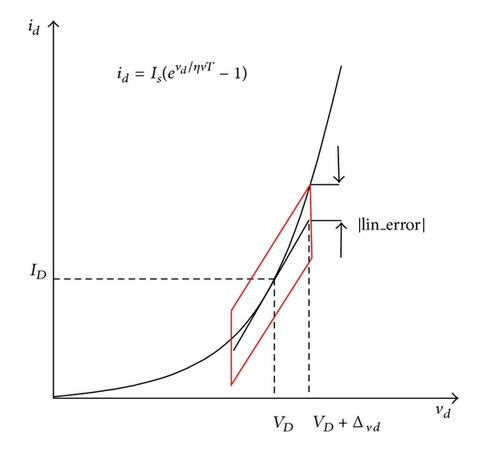

Figure 5(b) shows approximation of nonlinear diode (from Figure 5(a)) at the operating point.

3.4. Time-Domain Properties Modeled with Affine Arithmetic

To analyze system behavior it is necessary to specify values of its properties. In the following there will be given a list of properties in time, but also in frequency domain whose specified values can be modeled using Affine Arithmetic approach.

3.4.1. Settling Time Property

3.5. Frequency-Domain Properties Modeled with Affine Arithmetic

The properties determining system behavior in frequency domain, whose specified values can be modeled with Affine Arithmetic, refer to low pass filter design specifications.

3.5.1. The Allowed Ripple in the Pass Band

3.5.2. The Allowed Ripple in the Stop Band

4. Semisymbolic Simulation and Assertion-Based Verification

In order to reduce high number of simulation runs required for simulation of systems with parameter variations, semisymbolic simulation is introduced. The idea of this approach is to model parameter deviations using Affine Arithmetic and simulate systems including these deviations. The simulation result is range-based system response which can be obtained in only one simulation run. Semisymbolic simulation can be performed on two levels: system level and circuit level.

4.1. Semisymbolic Simulation on System and Circuit Level

For semisymbolic simulations on system level SystemC AMS environment is used. Affine Arithmetic is implemented in a separate library which is due to SystemC AMS C++ based nature very easily integrated.

- (1)

A netlist of a simulated system is converted into the according system of differential algebraic equations (DAE) using the Modified-Node-Analysis (MNA):

(22) -

where the vector represents the vector of time dependable state variables and represents the vector of time dependable circuit parameters.

- (2)

The equation system is passed through a numerical equation solver which performs DC, AC, and Transient Analysis [37]. The solver uses numerical methods as forward, backward Euler or trapezoidal methods to solve the equations.

Since at transistor level analog circuits are usually described with nonlinear differential algebraic equations the numerical solving is followed by linearization of equation system in the operating point with respect to variables and parameters. To deal with affine terms the algorithm [37] with the following steps is applied in the simulator.

In the first step the nominal solution is computed using Newton-Raphson method. In the second step the equation system is linearized in the operating point. Result of linearization is the linear dependency of variables according to the parameter deviations. In the case of linear system with constant parameters and variable inputs the result of linearized equation system is exact affine solution and algorithm ends. As the equation system usually contains nonlinear expressions, the affine solution of the linearized system is usually an underestimation of the exact solution, and therefore it has to be extended to include the exact area. This is done in the third step of algorithm.

4.2. Assertion-Based Verification with Affine Arithmetic

The verification technology proposed in this work is based on assertions which use Affine Arithmetic to model specified values of system properties as ranges. As simulation and verification environment SystemC AMS is used. The assertions representing specifications are verified within simulation run. In the case where the specification is violated the specification violation is reported and simulation run is stopped. To describe specifications with AAF+A, the set of operators defining the syntax of these assertions is used. Table 2 summarizes available operators whose meaning will be briefly described in the following.

| AAF+A operators | Symbols | Operator meaning |

|---|---|---|

| Arithmetic operators | ⊖∈{+, −, *, /, ∧} | Symbols for the usual arithmetic operations |

| Relation operators | ∙∈{<, >, ≤, ≥, = = } | The usual relation operations |

| Logic operators |

|

Logic and, or, implies not |

| Affine analog operator | IN | Compares two affine terms a and b |

| Affine analog frequency operator |

|

|

| Slope operator | DV | Calculates slope of a signal |

| Temporal operators | □∈{G, F } | Always, eventually |

| Affine analog time interval | Time ∈ AAF, time = t0 + εΔt, t0, Δt ∈ ℝ | Specified signal time interval of affine analog signal |

| Verification time interval | [t], t ∈ ℝ | Specified time within which the assertion is verified |

The label AAF in the table assigns the set of affine terms. The set of assertions based on Affine Arithmetic (AAF+A) is comprised of two sets. The first set defines Boolean formulas checking validation of properties in time-domain TBF and the second one in frequency domain FBF. The operators from Table 2, comprising, respectively, the sets TBF and FBF, are given in Table 3.

| TBF | FBF |

|---|---|

| s∙d ∈ TBF | {GFIN, FIN}(f1, f2, FFT〈N〉(β), γ) ∈ FBF |

| s - affine signal, d ∈ ℝ | f1, f2 ∈ ℝ, N ∈ℕ, β-affine signal, γ ∈ AAF |

| DV(s)∙d ∈ TBF | IN(ζ, ψ) ∈ FBF |

| s, affine signal, d ∈ ℝ | ζ ∈ FF, ψ ∈ AAF |

| IN{[time]}(φ, ϑ) ∈ TBF | c ∙ d ∈ FBF |

| φ ∈ {s, DV(s)}, time ∈ AAF, ϑ ∈ AAF | c ∈ FF∧d ∈ ℝ |

-

TBF ∪ FBF ⊂ AAF + A,

-

(α ∈ AAF + A∧t ∈ ℝ)→□(α) ∈ AAF + A∧□[t](α) ∈ AAF + A,

-

(α, β ∈ AAF + A) → α⊘β ∈ AAF + A∧!(α) ∈ AAF + A.

The following table (Table 4) gives a brief description of operators given in Table 2. If α and β represent the ranges modeled with Affine Arithmetic, then the operator ≤ in Table 4 assigns that the first range α lies in the second range β (α ⊂ β). If β is a real value, then this operator assigns that the upper bound of α is lower or equal to the real variable β.

| Operator | Explanation |

|---|---|

| IN(s, h) | Satisfied at time t′ in which (s(t′) ≤ h)) |

| IN[time](s, h) | Satisfied at time t′((t′ ∈ time) in which (s(t′) ≤ h)) |

| FIN(f1, f2, FFT(s), β) | Satisfied if ∃f ∈ [f1, f2]⇒FFT(s)(f) ≤ α |

| GFIN(f1, f2, FFT(s), β) | Satisfied if ∀f ∈ [f1, f2]⇒FFT(s)(f) ≤ α |

|

Satisfied if the formula h holds always or at least once during simulation, respectively |

5. Demonstration Examples

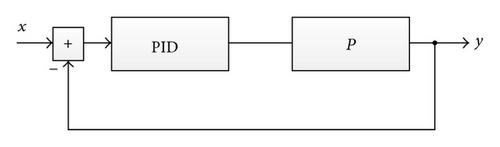

Within this work the applicability of the proposed verification method will be shown through several examples. The examples are chosen to demonstrate ability to handle typical challenges for symbolic simulation like feedback, nonlinearities, and discontinuities. Note that complexity itself is not a challenge by itself. As the first example a closed loop control system composed of a PID controller and a plant is chosen. Its block diagram is shown in Figure 6. Further, as the second example also a feedback system, which needs to set a room temperature to a certain value considering variation in the external temperature, is chosen. The third example through which the performance of the method will be illustrated is a PLL (Phase-Locked Loop) circuit containing the loop and nonlinear elements like a phase detector or a voltage controlled oscillator.

5.1. A Control System including a Parameter Uncertainty of a Plant

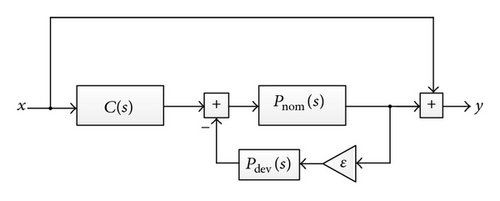

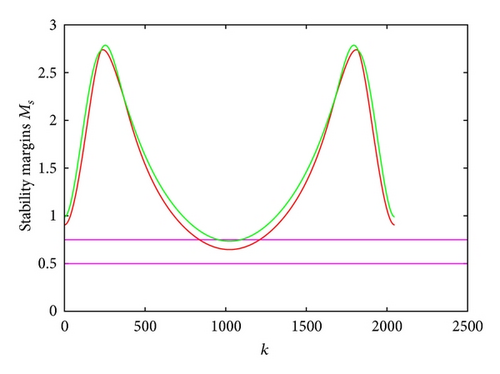

A control system including uncertainties meets the stability margin specification if its stability margin Ms lies in the range [0.5,0.75]. Since Ms is crucial to verify the control system against the given specification, the proposed verification method will use the system given in Figure 7 to calculate the stability margin Ms.

This assertion expresses that infimum with respect to frequency determined with min (FFT〈2048〉(h(t)) must always (assigned with operator G) lie in the range modeling the stability margin specification (0.625 + ε0.125) during simulation.

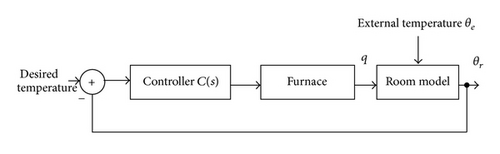

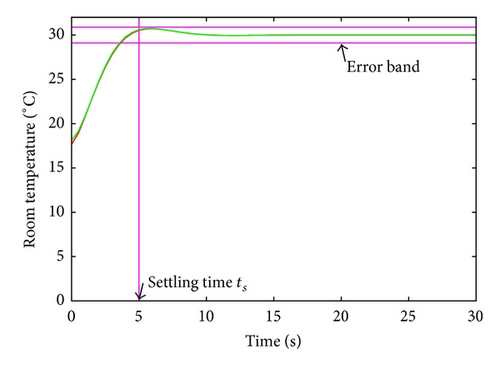

5.2. A Room Heating Control System

As the second demonstration example a system which controls a room temperature is chosen. The block diagram of the system is shown in Figure 8.

- (1)

if the room temperature θr within 5 seconds reaches the value varying within 3% of the final value,

- (2)

if the final value is reached.

The simulation results are given in Table 5 in Section 5.4.

| Example | Time without AAFA (s) | Time with AAFA (s) | Overhead (s) |

|---|---|---|---|

| The control system with parameter uncertainty | 17.6 | 19.5 | 1.9 |

| The room heating control system | 9.3 | 10.8 | 1.5 |

| PLL circuit | 7.3 | Simulation run stopped | — |

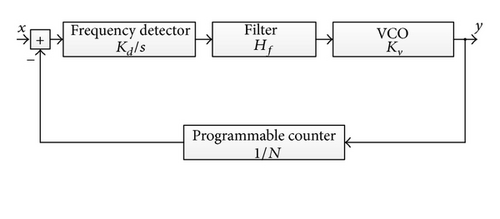

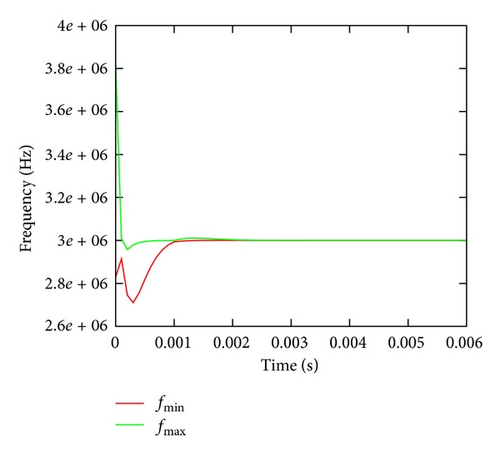

5.3. A PLL Circuit including Parameter Uncertainties

- (i)

in radio transmitters it is used to synthesize frequencies, which are a multiple of a reference frequency;

- (ii)

clock generators which multiply a low-frequency reference clock to higher operating frequencies of microprocessors;

- (iii)

in communication systems for coherent demodulation and demodulation of frequency and phase modulated signals.

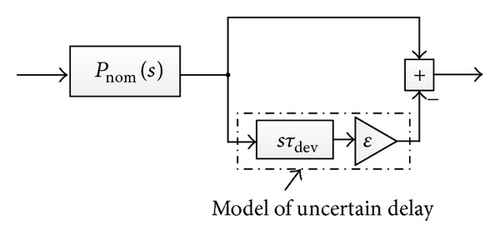

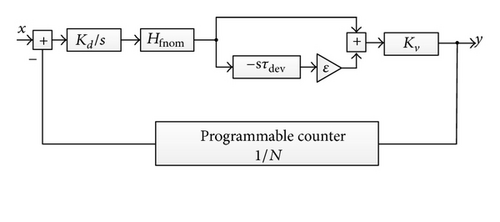

In this paper a PLL circuit as a frequency synthesizer is considered. Its block diagram is shown in Figure 9. This PLL model models the behavior of the system in ideal conditions. In reality certain numbers of deviations influence the behavior of the PLL causing design specifications to violate from their values previously defined by design. Since the PLL is often the part of more complex AMS systems (e.g., in the role as a frequency synthesizer it is embedded into communication systems to generate carrier frequencies) it is of a great importance to verify if the desired output behaviour in the presence of parameter deviations is still met. Within this work a time delay of the filter from Figure 9 will be considered and added to the PLL model.

The parameter τdev represents the maximum value of time delay which is for this example 100 μs. The block diagram of the PLL model considering the filter time delay is shown in Figure 10.

5.4. Experimental Results

The SystemC AMS is used as simulation and verification environment. The control system considering the filter parameter uncertainty was simulated and verified for 106 s with the sampling rate Ts = 1 s. The specification (Assertion 6) passed and the stability margin calculated for the control system is shown in Figure 11. The symbol k in the figure assigns the k frequency component of Fast Fourier Transform which was used to determine the stability margin with respect to frequency.

Using the sampling period Ts = 0.5 s the heating control system was simulated for 2*105 s. The system met desired requirements and both assertions (Assertions 8 and 9) passed. The signal representing the room temperature θr is shown in Figure 11.

The PLL circuit was simulated and verified for 20 s with the sampling period Ts = 0.1 ms. It was verified if the lock time of the PLL to switch from 2.9 MHz to within 5 kHz of 3 MHz is less than 1 ms. The Assertion 10 failed, and simulation run was stopped reporting the information about the specification violation. The fact that the PLL output frequency did not (within 1 ms) set to the desired value within the specified tolerance does not imply that it will not do so after some time. To prove this the PLL simulation result is given in Figure 12.

Since the assertion failed and the simulation run was stopped, the PLL response from Figure 12 is the result of simulation in the case where the assertion is omitted. From the figure it can be concluded that the output frequency converges to its final value and deviated terms converge to zero. This fact is one of the main advantages of the Affine Arithmetic approach. Its ability to identify the correlation between system quantities reaches its maximum in the systems with feedback loops like the case with our demonstration examples.

Hence, even in the case where the loop contains the nonlinear elements the additional terms (which are the result of overapproximation introduced by nonlinear operations) will have negligible values, and the output will converge to its finite value. To free the memory of unnecessary variables, the authors in [28] propose the (cleanup) method. Concretely, all terms under some user specified value are replaced with only two symbols, the one representing the sum of all terms with a positive and the other with a negative sign. In this way the safe inclusion of the result is kept, and the number of terms is drastically decreased.

Table 5 summarizes the simulation times necessary for all designs in the case where AAF+A assertions were included into design simulation and when they were omitted. It can be noted that in the case where the assertions were satisfied, the proposed verification method generated additional simulation time, but the overhead was not high.

The simulation time of the PLL in the case where the assertion was embedded into simulation was omitted. The reason lies in the fact that the assertion failed stopping the simulation process, and hence the time required for simulation was much lower than for the case in which the assertion was not included.

6. Conclusion and Future Work

This work introduces a methodology that enables verification of analog/mixed-signal systems including deviations. The verification method is combined with symbolic simulation which generates the worst case dependable response adding deviations to a system model and modeling them as ranges. Since the generated output behaviour contains all possible traces for the considered parameter set the proposed assertion-based technology can provide formal verification result using simulation-based techniques. The assertions use Affine Arithmetic to model allowed or forbidden areas of typical system properties as ranges. The specified ranges are further combined with Boolean logic, frequency operators, and temporal logic which allows us to verify the system behaviour in time, but also in the frequency domain. The assertions are embedded into simulation, and as soon as the assertion violation is detected, the simulation run is stopped, and information about the assertion harm is reported.

Overapproximation is a challenge that can become a problem for strongly nonlinear systems. The first step to deal with this problem was proposed in [28] and found its applicability in the systems containing the loops. The further step towards the problem solution is to modify Affine Arithmetic in the way that we keep the second order terms in symbolic representation and in this way that we reduce overapproximation.

Furthermore, the AAF+A assertions (Table 2) will be extended from rather formal operators to libraries of application-specific properties that are close to requirement specifications found in various application domains. Also, the method up to now verifies the system against the specifications for which time and frequency requirements must be known in advanced. One interesting direction in the future would be to extend the method to extract the information about lower and upper bounds of time or frequency for which the system behaviour is still desirable under the considered set of deviated parameters.

Acknowledgment

This work has been funded by the Vienna Science and Technology Fund (WWTF) through Project ICT08_012.